IC笔试:华为实习笔试

时间:2022-08-15 21:00:00

参考

1.对以下时序分析的正确描述是()

A.recovery时间是指异步控制信号在有效时钟到达后必须保持稳定的时间 B.基于数据到达时间和数据所需的时间,计算时钟信号的时间裕度

C.以下公式用于计算最大数据skew : Maximum Data Arrival Skew = Shortest Data Arrival Path - Longest Data Arrival Path

D.removal时间是指异步控制信号在有效时钟到达前必须保持稳定的最短时间

B

recovery time 对应Tsu; removal time对应Th

2、下列对于逻辑最小项的描述错误的是()

A.n变量有2^n项最小项。

B.两个不同的最小项之积为0。

C.最小项之和为0。

D.最小项中每个变量只能以原变量或反变量的形式出现一次。

C

三、常用工具ModelSim哪家公司的产品()?

A.Mentor

B.SpringSoft

C.Cadence

D.Synopsys

A

4.信号的抖动和漂移取决于( )区别的

A.抖动频率是否高于10Hz

B.分别表现在时间轴和幅度轴上

C.抖动幅度是否超过1/10信号周期

D.分别表现在幅度轴和时间轴上

ITU-T G.701标准将抖动定义为:抖动是指数字信号在短期内相对于理想位置的重要瞬时变化。. 还有一个跟抖动很类似的概念,即漂移。. 一般来说,抖动是指发生较快的定时偏差,而漂移是指发生较慢的定时偏差。. ITU将漂移和抖动之间的门限定义为10Hz,偏移频率大于10Hz抖动,小于10Hz称为漂移。

A

5.以下说法是正确的( )

A.时钟的边缘速率越快越好

B.数据信号只关注高低电平值,与高低电平数据的有效宽度关系不大

C.数据信号要求边缘必须单调,无回沟和台阶

D.采样时钟信号采样沿不能回钩,台阶

A:时钟边缘不是越快越好,目前FPGA时钟最多为百兆赫兹级,时钟过快,不利于数据存储和时序分析。

B:数据信号的高低电平持续时间非常重要,可以联想到建立维持时间的概念,数据必须稳定存在一段时间。

C:数据的边缘特性并不重要,重要的是其高低电平保持稳定的持续时间。边缘是否稳定并不重要。

D:采样时钟的边缘特性非常重要,因为采样时钟的价值是在边缘时刻启动和捕获数据,所以对边缘特性要求很高,不能有台阶和回钩。

D

6.对时钟的描述是错误的( )

A.所谓行波时钟,就是用寄存器的输出作为另一个寄存器的时钟输入

B.全局时钟是所有逻辑公用的时钟源,建议尽量使用全局时钟

C.局部时钟是部分逻辑使用的时钟源。建议按需使用局部时钟

D.门控制时钟使用控制门电路的能量信号控制时钟打开和关闭。当时钟关闭时,停止相应的时钟域可以实现节能。因此,建议只使用组合逻辑在模块代码中生成门控制时钟。

吾见:D

理由:

A:就是行波时钟的概念。又叫 涟漪时钟 。

B:全局时钟有利于时序的分析和综合。

C:正确。

D:门控时钟只用组合逻辑实现,会产生很大的毛刺问题。

7、关于CPLD和FPGA说法有误:()

A.不同粒度的逻辑单元,设计灵活性相同。FPGA逻辑单元的粒度比CPLD小,所以设计更灵活

B.FPGA芯片的逻辑门密度比CPLD高

C.CPLD采用线段连接开关结构,内部连接长度积累;FPGA采用交叉开关结构,内连率高,内连长度不积累

D.虽然CPLD与FPGA数字逻辑电路可以集成成千上万门,但是CPLD更适合完成各种组合逻辑FPGA逻辑电路更适合完成更多的时间序

C 选项,FPGA是非连续布线,分线段互联,延迟不可控,连接长度可累积。CPLD是连续布线,延迟严格可控。

8.射级跟随器的特点是()

A.输入阻抗低,输出阻抗低

B.输入阻抗高,输出阻抗高

C.输入阻抗低,输出阻抗高

D.输入阻抗高,输出阻抗低

理由:

射极跟随器是共集电极放大电路,其主要功能是放大交流电流,以提高整个放大电路的负载能力。在实际电路中,通常用作输出级或隔离级。

其特点是输入阻抗高,输出阻抗低,信号源电流小,负载能力强,常用于多级放大电路输入输出水平,也可连接两个电路,减少直接连接的影响,缓冲。

虽然射极跟随器电路没有电压放大,但仍有电流放大,因此有功率放大。

射极跟随器电路的主要特点是输入电阻高,传输信号源信号效率高;输出电阻低,负载能力强;电压放大倍数小于1,接近1,输出电压与输入电压相同,具有跟踪特性,广泛应用于输出级或中间隔离级。

9、4bit二进制计数器,其翻转率(Toggle Rate),按100%计算每时钟翻转)约为()

A.0.3

B.0.125

C.0.5

D.0.47

0000(0.25) 0001(0.5) 0010(0.25) 0011(0.75) 0100(0.25) 0101(0.5) 0110(0.15) 0111(1) 1000

sum / 8

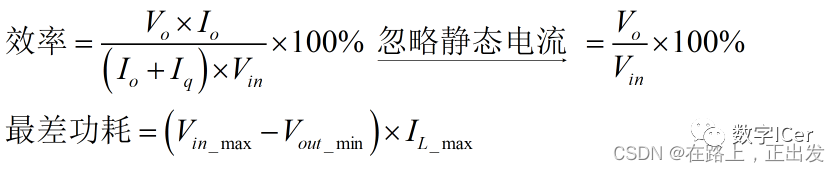

10、LDO电源Vin为5V,Vout为3V,输出电流为0.5A,最大耗散功率2W,电源效率为

A.0.6

B.0.5

C.0.75

D.不知道电流,不能计算

理由:

LDO即低压差 线性 稳压器。相关公式:

11、请选出哪个不是当前FPGA的加载方式

A.被动并行

B.主动串行

C.JTAG

D.I2C加载

12、UVM树形结构的根是

A. uvm_env

B. uvm_test

C. uvm_object

D. uvm_top

13.对过程赋值的以下描述不正确

A.在非阻塞过程赋值中,目标赋值是非阻塞(因为延迟),但可以预定在未来某个时间同步发生(根据延迟;如果是0延迟,则在当前时间步骤结束)

B.非阻塞性过程赋值在所有句子执行前执行

C.赋值符号用于非阻塞性过程赋值"<=”

D.赋值操作符是"="过程赋值是阻塞性过程赋值

B

14.时序逻辑电路不属于以下电路

A.分频器

B.加法器

C.全加器

D.计数器

BC

16.芯片的工作功耗与()无关

A.工艺

B.工作频率

C.电压

D.工作时间

D

在下列调度算法中,绝对优先调度算法有()

A.RR

B.DRR

C.SP

D.WRR

C

19.分组转发芯片需要支持40G以太网64字节短包线速,250M工作时钟,需要大约 ( ) (考虑帧间隙&前导码)。

A.16拍

B.12拍

C.3拍

D.4拍

理由:

帧间距,12字节;

前导码:8字节。

帧长:64字节。

(12 8 64)×8=84×8=672bit/Packet;

40G /〔(64 8 12)×8〕= 59.5238Mpps;

250 / 59.5238 = 4.2

20、在Verilog HDL()对操作符的优先描述是正确的

A.逻辑与(&&)操作符优先级高于逻辑或(I)操作符

B.按拉异或(^)操作符优先级高于一元逻辑非()

C.一元逻辑非操作符优先于右移操作符

D.小于操作符的优先级高于和(&)操作符

CD

在以下描述中,()不属于面向对象思想的主要特征

A.封装性

B.多态性

C.继承性

D.跨平台性

D

以下是什么?FPGA开发工具

A Quartus

B.其他都是

C. Vivado

D.ISE

B

23、时序电路的基本时间参数有

A.建立时间、保持时间、最大工作频率

B.建立时间、保持时间、访问周期

C.上升时间、下降时间、传输延迟时间

D.上升时间、下降时间、最大工作频率

A

24、综合编译有时会报错: cannot find module"xxx_ram",引起error的原因是()

A.xxx__ram.v文件中有语法错误

B.xxx_ram module中有语法错误

C.xxx_ram module没有添加到综合列表中

D.xxx_ram.v没有添加到综合列表中

25、对于序列的傅立叶变换而言,其信号的特点是

A.时域离散非周期,频域连续周期。

B.时域离散周期,频域连续非周期;

C.时域离散非周期,频域连续非周期;

D.时域连续非周期,频域连续非周期;

A

理由:

序列本身应该是离散的,直接排除D,另外,根据DSP的知识,

时域和频域,一个域的离散对应另一个域的周期,一个域的连续对应另一个域的非周期。

26、下列关于工具综合过程描述不正确的是()

A.综合工具具备等价寄存器优化功能

B.综合工具具备将连续打拍的寄存器映射为移位寄存器的功能

C.综合工具可以自动提取状态机

D.综合工具不关心设计的主频约束

D

27、K=M&N,如果M为’x’态,那么K=

A.×

B.0

C.z

D.1

A

28、负反馈的优点不包含

A.改善放大器的线性和非线性失真

B.改变输入电阻和输出电阻

C.具有自动调节功能

D.提高放大器的增益

D

理由:

负反馈增益略有下降。

29、下面哪个不是Verilog保留字

A. large

B.container

C.supply

D. force

B

30、a=1’b1;b=5’h10;那么{a,b}

A.5’h30

B.6’b11000

C.6’h110

D.6’h30

D

31、关于复位下列哪种说法正确

A.根据使用的器件和需求选择异步复位还是同步复位

B.同步复位增加了时序收敛的难度

C.同步化异步复位可以保证逻辑正确复位

D.异步复位易受毛刺影响从而导致逻辑错误

A C D

32、以下关于综合、布线说法正确的是()

A.使用管脚的电平、电流强度、翻转速率以及上下拉设置正确。

B.所有综合布线分析过程中,出现的warning和info信息都需要确认。

C.对端芯片如果三态输出,逻辑输入管脚需要设置上下拉电阻,确保其信号在不被驱动时,逻辑误采样

D.所有接口时序都要有时序分析报告,指导进行时序设置。

E.综合后的时序报告不需要关注,只要布线后时序可以过就可以了

A B C D

33、下面哪些说法是错误的?

A.当一个数据字的1个数为偶数时称为奇校验;这个数据若出现奇数个1,则有奇数个bit出错

B.当采用奇校验后,接收端接收数据有偶数个1,则这个数据肯定是有偶数个bit发生错误

C.当一个数据字的各个二进制bit的模二加为0时表示偶校验

D.当一个数据字的0个数为偶数时称为奇校验

A B D

34、a=3’b010,b=3’b101下面哪个语句得到的计算结果为1

A. |(a&b)

B.!(a^b)

C.^(a|b)

D.(|(a+b))

C D

35、下列哪些语言可以用来开发或验证FPGA逻辑模块

A. system verilog

B.verilog

C.C++

D.C

AB

36、基本微分电路存在的问题有()

A.基本微分电路可能引起自激振荡

B.基本微分电路的RC环节对于反馈信号具有滞后作用

C.当输出电压发生突变时,可能导致基本微分电路不能正常工作

D.基本微分电路抗干扰性能差

ABCD

37、下列方法对于设计提升系统时钟频率有帮助的有() 。

A.减小core供电电压

B.升高器件工作温度

C.减少组合逻辑级数

D.采用pipeline设计

BCD

38、相对于ASIC,FPGA应用于产品有如下优势:

A.更高的时钟频率

B.更低的功耗

C.更快的上市时间

D.小批量产品,成本更低

cd

39、FPGA内使用相同时钟沿的同步数字电路,最高频率和哪些因素有关?

A.时钟的占空比

B.D触发器组成pipeline长度

C.时钟skew

D.逻辑块间互连布线长度

bcD

40、Quartusll中的Pin Planner视觉工具为引脚和引脚组分配提供了一种途径。它包括的内容为

A.器件的封装视图

B.以不同的颜色和符号表示不同类型的引脚

C.已分配和未分配引脚的表格

D.以其他符号表示l/O块

ABCD