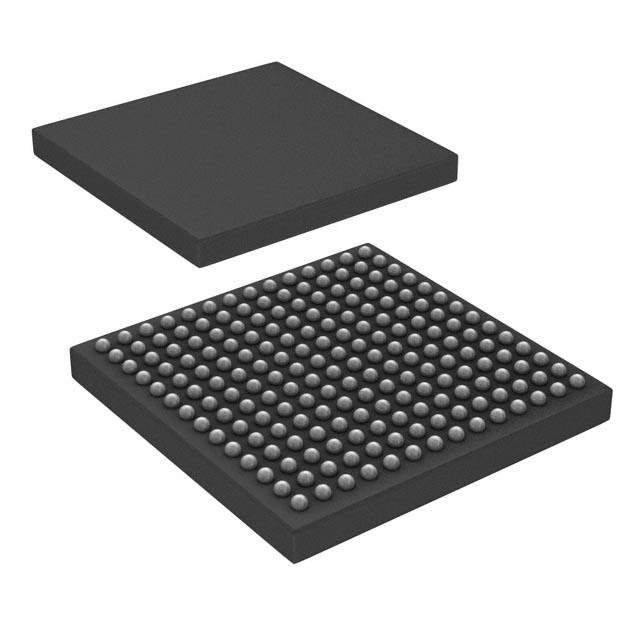

AD6679BBPZRL7-500

RF Receiver 1.25V/2.5V/3.3V 196Pin BGA T/R

Product Details

The AD6679 is a 135 MHz bandwidth mixed-signal intermediate frequency IF receiver. It consists of two, 14-bit, 500 MSPS analog-to-digital converters ADCs and various digital signal processing blocks consisting of four wideband DDCs, an NSR, and VDR monitoring. It has an on-chip buffer and a sample-and-hold circuit designed for low power, small size, and ease of use. This product is designed to support communications applications capable of sampling wide bandwidth analog signals of up to 2 GHz. The AD6679 is optimized for wide input bandwidth, high sampling rates, excellent linearity, and low power in a small package.

The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations.

Applications

- .

- Diversity multiband, multimode digital receivers

3G/4G, TD-SCDMA, W-CDMA, GSM, LTE, LTE-A

- .

- DOCSIS 3.0 CMTS upstream receive paths

- .

- HFC digital reverse path receivers

### Features and Benefits

- .

- Parallel LVDS DDR outputs

- .

- In-band SFDR = 82 dBFS at 340 MHz 500 MSPS

- .

- In-band SNR = 67.8 dBFS at 340 MHz 500 MSPS

- .

- 1.1 W total power per channel at 500 MSPS default settings

- .

- Noise density = −153 dBFS/Hz at 500 MSPS

- .

- 1.25 V, 2.50 V, and 3.3 V dc supply operation

- .

- Flexible input range: 1.46 V p-p to 2.06 V p-p 2.06 V p-p nominal

- .

- 95 dB channel isolation/crosstalk

- .

- Amplitude detect bits for efficient automatic gain control AGC implementation

- .

- Noise shaping requantizer NSR option for main receiver function

- .

- See data sheet for additional features