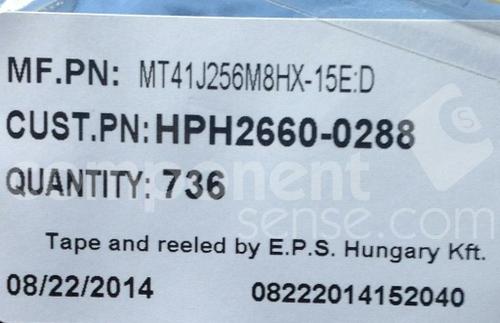

MT41J256M8HX-15E:D

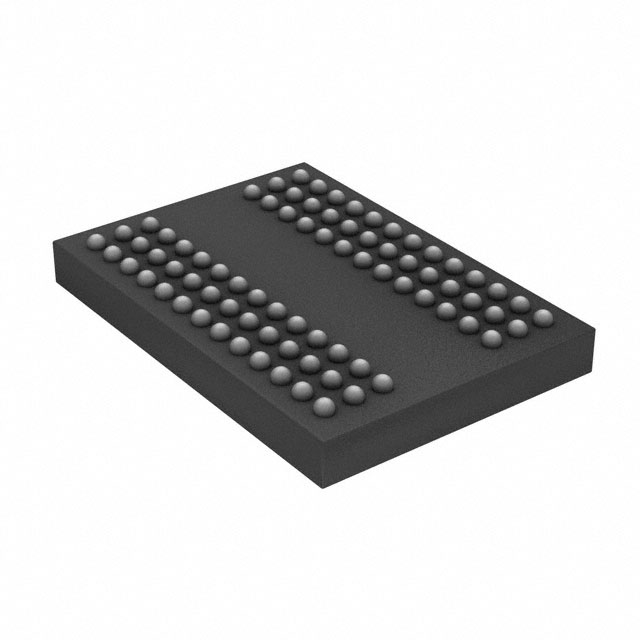

DRAM Chip DDR3 SDRAM 2Gbit 256Mx8 1.5V 78Pin FBGA

DDR3 SDRAM

2Gb: x4, x8, x16 DDR3 SDRAM

Features

• VDD= VDDQ= 1.5V ±0.075V

• 1.5V center-terminated push/pull I/O

• Differential bidirectional data strobe

• 8n-bit prefetch architecture

• Differential clock inputs CK, CK#

• 8 internal banks

• Nominal and dynamic on-die termination ODT for data, strobe, and mask signals

• Programmable CAS READ latency CL

• Posted CAS additive latency AL

• Programmable CAS WRITE latency CWL based on tCK

• Fixed burst length BL of 8 and burst chop BC of 4 via the mode register set [MRS]

• Selectable BC4 or BL8 on-the-fly OTF

• Self refresh mode

• TC of 0°C to 95°C

– 64ms, 8192 cycle refresh at 0°C to 85°C

– 32ms, 8192 cycle refresh at 85°C to 95°C

• Self refresh temperature SRT

• Write leveling

• Multipurpose register

• Output driver calibration