MEMORY系列之DDR设计规则

时间:2023-10-30 08:37:02

1、SCH设计原则

DDR目前原理图的设计比较成熟,因为它的信号引脚是固定的,有统一的规范(JESD而且像Micron、Samsung、SK Hynix、Toshiba等厂家都有自己的technical note,因此,本文只列出了一些特殊的注意事项。

1.1.颗粒容量的可扩展性

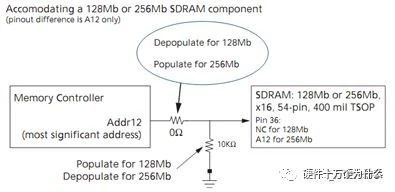

根据JEDEC标准,不同容量的内存芯片一般与引脚兼容。为了实现电路板的可扩展性,可以做以下处理,如128Mb与256Mb兼容应用。

1.2、未用的DQ引脚处理

对于x16的DDR对于设备,未使用的引脚应进行一定的处理。x16的DDR来说,DQ[15:8]如果不使用,处理如下,相关的UDM/DQMH拉高用于屏蔽DQ线,DQ[15:8]通过1~10k电阻接地用于防止爆发时的噪音

1.3、端接技术

DDR常用的端接技术有以下两种:

串行端接,主要用于负载DDR当颗粒不超过4个时。I/O信号来说,例如DQ,串行端接电阻Rs放置在线路中间,抑制振铃、过冲和下冲。对于对于单向信号,如地址线、控制线、串行端接电阻放置在线路中间或信号发送端,建议放置在信号发送端。

并行端接,主要用于负载SDRAM设备大于4个,线长>2inch,或通过模拟验证需要并行端接。并行端接电阻Rt取值大约为2Rs,Rs取值范围为10~ 33ohm,故Rt取值范围为22~66ohm。并行端接电压为VTT。

对于没有ODT功能的DDR,需要使用所有数据线、地址、命令和控制线single-ended Parallel Termination端接。

1.4、时钟信号

所有DDR差分时钟线CK与CK#必须在同一层布线,误差±20mil,内层布线最好抑制EMI。若有多个系统DDR如果设备使用电阻值100~200ohm差分端接的电阻。

若时钟线的分叉点到DDR设备的接线长度<1000mil,要使用100~120ohm如下图所示:

若时钟线的分叉点到DDR设备的接线长度>1000mil,要两个使用200240ohm由于两个2000电阻差端接240ohm电阻并联值正好是100~120ohm。如下图所示。

针对一拖多的情况,在时钟线差分对之间经常会并联一个pF根据阻抗匹配的观点,差分电容的容值需要匹配差分阻抗Z0,故,即800MHz时钟、100Ω当差分阻抗时,C约为2pF。为了过滤差模干扰,消除反射,电容器通常放置在发送端。

1.5、参考电压VREF

轻负荷(<4片DDR可使用以下方法:

VREF走线尽量短粗;

在器件VREF将0放在引脚处.1uF旁路电容;

在VREF和VDDQ之间放一个0.1uF的电容(上电时电压的跟随特性更好);

在VREF和VSSQ之间放一个0.1uF的电容;

如下图所示:

重载(>4片DDR可使用的设备)IC来产生VREF。

IC两种电压集成在内部VTT和VREF,其中VTT最高电流可达3.5A,平均电流为0A,VREF的电流比较小,一般只有3mA左右。

Appropriate DDR termination regulator vendors offering products with VTT, VREF, VDDQ, and VDD outputs include:

Fairchild—ML6554and FAN1655

LinearTechnology—LTC3413 and LTC3831

NationalSemiconductor—LP2995 and LP2996

Phillips—NE57810 and NE47814

TI—TPS51200

1.6、VTT设计

当数据线地址线负载较重时,VTT临态电流峰值可达3.5A这种临态电流的平均值约为0A。在某些情况下不需要VTT技术(并行端接):

有两个或更少的系统DDR

总线所需的电流不是很高,大约中等

无需通过仿真验证

VTT一般用于产生电压IC,厂商包括:Intersil,Philips Semiconductors, Fairchild,National, TI等等。

选用IC实现VTT,建议使用以下原则:

- 地址/控制/命令信号线Rt端接到VTT,VTT=VDD/2

- VTT时钟信号线不端接,时钟信号线采用差异端接技术

- VTT与VREF同一层必须有150个布线平面mil推荐它们在不同层次的距离

- VTT布线平面至少需要24个.7uF2个1000的去耦电容uF电容。具体位置是电容。VTT的两个端点(at each end)

- VTT表面布线宽度至少为15mil,推荐250mil

- 上电时序:VTT必须在开始上电VDDQ之后(具体实现方法可以采用VDDQ来控制VTT电源芯片的使能),避免器件latch-up,推荐VTT和VREF同时上电

如果线路需要分支,建议使用T型分支。

见下图:

1.7.引脚交换特性

同组(Lane)数据线可以交换。

原因是内存数据线只存储数据,而CPU是根据CPU存取的数据线与内存的数据线顺序无关,相当于将数据存储在一组容器中,数据按顺序放置。有时为了方便布线,调整组中的顺序。

无法交换地址线。原因是模型寄存器的值是通过地址总线(通过A4~A6配置模式寄存器)。

2、PCB设计规则

2.1、布局

首先要确定DDR拓扑结构,一般而言,DDR1/2采用星形结构,DDR3.菊花链结构(不是所有)DDR3都可以用Fly by结构,如果主控芯片不支持读写平衡(Read and WriteLeveling)不能使用功能Fly by因为Fly by结构的DQS和CK不等长!!!没有write leveling就没法调整DQS和CK两者之间的偏差。))。

扩展结构只影响地址的走线方式,不影响数据线。

星形拓补就是地址线走到两片DDR中间再向两片DDR分别走线,菊花链就是用地址线把两片DDR“串起来”。

DDR2是采用T形拓扑结构,这种结构是不是星形结构的删减版?采用T形拓扑是因为时序要求信号要同时到达。

那DDR3采用的Fly by结构,其实就是stub较短的菊花链,之所以采用此种结构是因为DDR3多了读写平衡的新技能,即使你们不同时到达,也能把它调过来。所以采用何种拓扑结构首先要看时序要求。

确定了DDR的拓补结构,就可以进行元器件的摆放,有以下几个原则需要遵守:

-

原则一,考虑拓补结构,仔细查看CPU地址线的位置,使得地址线有利于相应的拓补结构;

-

原则二,地址线上的匹配电阻靠近CPU(发送端);

-

原则三,数据线上的匹配电阻靠近DDR;

-

原则四,将DDR芯片摆放并旋转,使得DDR数据线尽量短,也就是,DDR芯片的数据引脚靠近CPU;

-

原则五,如果有VTT端接电阻,将其摆放在地址线可以走到的最远的位置。一般来说,DDR2不需要VTT端接电阻,只有少数CPU需要;DDR3都需要VTT端接电阻。

-

原则六,DDR芯片的去耦电容放在靠近DDR芯片相应的引脚。

以下是DDR2的元器件摆放示意图(未包括去耦电容),可以很容易看出,地址线可以走到两颗芯片中间然后向两边分,很容易实现星形拓补,同时,数据线会很短。

不带VTT端接电阻的布局图如下:

带VTT端接电阻的布局图如下:

带VTT端接电阻的情况,地址线上没有串联匹配电阻(DDR3),VTT端接电阻摆放在地址线可以到达的最远距离。

如果有数据线匹配电阻则必须靠近DDR放置。

以下是DDR3的元器件布局图,这里使用的CPU支持双通道DDR3,所以看到有四片(参考设计是8片)DDR3,其实是每两个组成一个通道,地址线沿着图中绿色的走线传递,实现了菊花链拓扑。

地址线上的VTT端接电阻摆放在了地址线可以到达的最远的地方。同样地,数据线上的端接电阻也放置在了靠近DDR3芯片的位置,数据线到达CPU的距离很短。同时,可以看到,去耦电容放置在了很靠近DDR3相应电源引脚的地方。

2.2、布线

2.2.1、设置线宽与线距

DDR走线线宽与阻抗控制密切相关,经常可以看到很多同行做阻抗控制。

对于纯数字电路,完全有条件针对高速线做单端阻抗控制;但对于混合电路,包含高速数字电路与射频电路,射频电路比数字电路要重要的多,必须对射频信号做50欧姆阻抗控制,同时射频走线不可能太细,否则会引起较大的损耗,所以在混合电路中,往往舍弃数字电路的阻抗控制。

DDR的供电走线,建议8mil以上,在Allegro可以针对一类线进行物理参数的统一设定,可以建立PWR-10MIL的约束条件,并为所有电源网络分配这一约束条件。

间距的控制要考虑阻抗要求和走线的密度。

通常采用的间距原则是2W或者3W。如果有足够的空间来走线,可以将数据线按3W的间距来走,可以减小很多串扰。

如果实在不行至少要保证2W的间距。除此之外**,数据线与其它信号线的间距至少要有3W的间距,如果能更大则更好**。

时钟与其它的信号线的间距至少也要保持3W,并尽可能的大。绕线的间距也可以采用2W和3W原则,应优先用3W原则。

相邻两层尽量参考GND。对于线间距,也可以在Allegro中建立一种约束条件,为所有DDR走线(XNET)分配这样的约束条件。

还有一种可能需要的规则,就是区域规则。Allegro中默认的线宽线距都是5mil,在CPU引脚比较密集的时候,这样的规则是无法满足的,这就需要在CPU或DDR芯片周围设定允许小间距、小线宽的区域规则。

2.2.2、设置等长规则

对于数据线,DDR1/2与DDR3的规则是一致的:

每个BYTE与各自的DQS,DQM等长,即DQ[0:7]与DQS0,DQS0N,DQM0等长,DQ[8:15]与DQS1,DQS1N,DQM1等长,以此类推。

地址线方面的等长,要特别注意,DDR1/2与DDR3是很不一样的。

对于DDR1/2,需要设定每条地址到达同一片DDR的距离保持等长。

对于DDR3,地址线的等长往往需要过孔来配合,具体的规则均绑定在过孔上和VTT端接电阻上。可以看到,CPU的地址线到达过孔的距离等长,过孔到达VTT端接电阻的距离也等长。

2.2.3、走线及等长

走线注意事项如下:

-

所有走线尽量短;

-

走线不能有锐角;

-

尽量少打过孔;

-

保证所有走线有完整的参考平面,地平面或电源平面都可以,对于交变信号,地与电源平面是等电位的;

-

尽量避免过孔将参考面打破,不过这在实际中很难做到;

-

走完地址线和数据线后,务必将DDR芯片的电源脚,接地脚,去耦电容的电源脚,接地脚全部走完,否则在后面绕等长时会很麻烦。

-

一般来说,DQ,DQS,DM和时钟信号线选择VSS作为参考平面,因为VSS比较稳定,不易受到干扰,地址/命令/控制信号线选择VDD作为参考平面,因为这些信号线本身就含有噪声。

完成等长规则的设定后,最后一步也是工作量最大的一步:绕等长。

在这一步,我认为只有一点规则需要注意:尽量采用3倍线宽,圆弧绕等长。

绕等长完成后,最好把DDR相关网络锁定,以免误动。

DDR数据线用DQS来锁存,因此要和DQS保持等长。

地址、控制线用时钟来锁存,因此要和时钟保持等长,一般等长就没有什么问题。

阻抗方面,一般来说DDR需要60欧姆,DDR2需要50欧姆,走线不要打过孔,避免阻抗不连续。串扰方面,只要拉开线距,一层信号一层地,就不会出问题。

无论是PCB上使用芯片还是采用DIMM条,DDRx(包括DDR3,DDR4等)相对于传统的同步SDRAM的读写,主要困难有三点:

第一,时序。由于DDR采用双沿触发,和一般的时钟单沿触发的同步电路,在时序计算上有很大不同。DDR之所以双沿触发,其实是在芯片内部做了时钟的倍频,对外看起来,数据地址速率和时钟一样。为了保证能够被判决一组信号较小的相差skew,DDR对数据DQ信号使用分组同步触发DQS信号,所以DDR上要求时序同步的是DQ和DQS之间,而不是一般数据和时钟之间。另外,一般信号在测试最大和最小飞行时间Tflight时,使用的是信号沿通过测试电平Vmeas与低判决门限Vinl和和高门限Vinh之间来计算,为保证足够的setup time和hold time,控制飞行时间,对信号本身沿速度不作考虑。而DDR由于电平低,只取一个中间电平Vref做测试电平,在计算setup time和hold time时,还要考量信号变化沿速率slew rate,在计算setup time和hold time时要加上额外的slew rate的补偿。这个补偿值,在DDR专门的规范或者芯片资料中都有介绍。

第二,匹配。DDR采用SSTL电平,这个特殊buffer要求外接电路提供上拉,值为30~50ohm,电平VTT为高电平一半。这个上拉会提供buffer工作的直流电流,所以电流很大。此外,为了抑制反射,还需要传输线阻抗匹配,串连电阻匹配。这样的结果就是,在DDR的数据信号上,两端各有10~22ohm的串连电阻,靠近DDR端一个上拉;地址信号上,发射端一个串连电阻,靠近DDR端一个上拉。

第三,电源完整性。DDR由于电平摆幅小(如SSTL2为2.5V,SSTL1为1.8V),对参考电压稳定度要求很高,特别是Vref和VTT,提供DDR时钟的芯片内部也常常使用模拟锁相环,对参考电源要求很高;由于VTT提供大电流,要求电源阻抗足够低,电源引线电感足够小;此外,DDR同步工作的信号多,速度快,同步开关噪声比较严重,合理的电源分配和良好的去耦电路十分必要。

2.2.4、DDR4布线(Tabbed Routing)

DDR4有一种特殊的布线方式:Tabbed Routing,Tabbed routing由intel公司2015年3月份提出,主要用在下一代处理器SKYLAKE平台,DDR4的走线方式。TabbedRouting主要的方法是在空间比较紧张的区域(一般为BGA区域和DIMM插槽区域),减小线宽,而增加凸起的小块(Tab),这种方法可以增加两根线之间的互容特性而保持其电感特性几乎不变,而增加的电容可以有效控制每一层的的阻抗,减小外层的远端串扰。该方法对阻抗和远端串扰可以很好的平衡,对于Tab的尺寸,需要根据实际PCB做详细的仿真设计,Intel也提供了一些Tool可以参考。

Tabbedlines have been proposed to reduce or eliminate FEXT(Far-end Crosstalk).

Tabbed Routing详细可参见《Intel: Crosstalk Mitigation andImpedance Management Using Tabbed Lines》一文.

除了JESD79系列规范,还可以参见Micron(TN-46系列、TN-41系列)文档。

本文转自--------硬件助手