国民技术面试20200910

时间:2023-01-17 06:30:01

202009年国民技术电话面试

1.两级运输中零极点的位置?主极点在哪里,次极点在哪里?加入密勒补偿后如何变化?如果电流增加,会发生什么变化?

第一个极点在第二个输入和输出之间,第二个极点在第二个输出。加入密勒电容后,主极点电容增加(1 A)Cc,因此,主极点靠近原点,次极点等效电容式(1 1/A)Cc,然而,在高频时,密勒电容被视为短路。此时,输出阻抗从RL减小为1/gm,因此,次极点将原点。当电流增大时,此时gm此时输出阻抗会变小,次极点会远离原点位置,系统会变得更加稳定。

2.大信号输入和小信号输入的输出波形是什么?

大信号输入,如果超过压力摆动率的限制,则输出波形为斜线,如果不超过压力摆动率的限制,则表示指数形式。小信号输出是指数形式

3.噪音应该如何降低?会有什么影响?

首先,共源共格栅上的噪声可以忽略,因为共源噪声可以忽略,而共格栅不产生噪声。除增益外,二级噪声为等效输入噪声,一级主要提供增益。因此,二级噪声可以忽略。主要噪声源是输入管的噪声。通过增加输入管的尺寸,增加面积可以降低噪声,但会增加寄生电容器,通过增加面积可以降低失衡电压。减少工艺失配.

(E-MOSFET指增强型,一般采用增强型设备。耗尽设备阈值电压为负,电压等于0,一般不使用。以下设备仅用于增强型)

4.温度升高迁移率,阈值电压如何变化?

迁移率和阈值电压降低,温度升高,载流子散射运动增强,载流子碰撞概率增加。因此,根据公式\(μ=v/E\),速度下降,迁移率下降。

阈值电压,阈值电压是使半导体表面产生反形层(导电沟)所需的栅极电压。当温度T升高时,半导体Fermi能导体将倾向于禁带中央变化Fermi势ψB减少更容易实现ψs≥2ψB因此,阈值电压降低。

此外,N半导体费米能级靠近导带,增加掺杂浓度可能导致费米能级进入导带,P半导体费米能级靠近价带,增加混合浓度可能导致费米能级进入价带。因此,增加混合浓度、费米能级与禁区中心之间的电势φB增大,所以φs>2φB,反型层的电势增加,即所需的栅极电压增加,阈值电压增加。

5.为什么短沟?MOSFET饱和源-漏电流不完全饱和?

对于短沟道MOSFET,输出源-漏电流饱和的原因基本上有两个:一是沟夹断引起的电流饱和;二是速度饱和引起的电流饱和。

对于沟夹的饱和度,由于夹的长度会随着上电压的增加而增加,剩余沟的长度也会随着源泄漏电压而缩短,导致源泄漏电流随源泄漏电压相应增加,输出电流不完全饱和。然而,这种电流不饱和的程度与沟长有关:对于长沟MOSFET,与整个通道长度相比,可以忽略这种夹紧区域长度随源-漏电压的变化,因此通道夹紧后的源-漏电流近似饱和;但对于短通道MOSFET,与整个沟长相比,这种夹长随源-漏电压的变化不容忽视,因此,随着源漏电压的增加,沟夹断后的源漏电流会明显增加-不饱和。

对于速度饱和引起的电流饱和,一般来说,当电场强、载流子饱和时,源漏电压不会进一步增加。因此,饱和电流原则上与源漏电压无关。

对于短沟道MOSFET,电流不饱和的另一个重要原因是所谓的DIBL(漏极感应源端势垒降低)效应。由于源区与通道之间总是存在高低结引起的势垒,当源漏电压越高时,通过通道的源漏电流越大,输出电流不会饱和。(DIBL:漏端电压的升高有助于将电子吸引到格栅极氧化层下方,因此格栅极所需的电压降低,阈值电压降低。VDS由于阈值电压下降,漏电流会上升)

总之,导致短沟MOSFET电流不饱和的主要因素是沟长调节效应和DIBL效应

6、为什么MOSFET饱和源-漏电流与饱和电压的平方关系?

增强型MOSFET(E-MOSFET)饱和源-漏电流表示式为 饱和电压(VGS-VT)是沟夹断时的源泄漏电压。MOSFET的转移特性(IDsat~VGS)曲线上,E-MOSFET饱和源-漏电流IDsat与饱和电压(VGS-VT)关系是抛物线。造成这种平方关系的原因有二:

①饱和源-漏电流越大,饱和电压越高;

②电流饱和对应于沟夹断,夹断区为耗尽层,宽度与电压之间存在平方根关系,导致上述平方结果。MOSFET电流-电压关系如此平方,因此常称为平方率装置。

为什么一般?MOSFET的饱和源-漏电流具有负的温度系数?

漏电流公式:KP,μ(主要是晶格振动散射),Vth它们都是负温度系数,随着温度的升高而,唯一的热电压VT正温度系数随着温度的升高而升高。事实上,在低温下Vgs当电流上升时,阈值电压器起主导作用Vgs迁移率主导,电流下降,当两者下降程度相同时,电流不变。

根据上述阈值电压和载流子迁移率的不同影响MOSFET可以知道饱和电流的表示式:

①当饱和电压(VGS-Vth)较大(即VGS>>Vth)当阈值电压温度关系的影响可以忽略时,输出源-泄漏电流的温度特性将主要取决于负温度系数(温度升高、大)VGS,迁移率起主要作用,迁移率下降,IDS下降);

②当饱和电压(VGS-Vth)较小(即VGS~Vth)当输出源-漏电流的温度特性主要取决于阈值电压的温度关系,从而具有正温度系数(温度升高,小VGS,阈值电压起主要作用,阈值电压下降,IDS也增大)。

一般的MOSFET,为了获得更大的跨导,饱和电压经常被压制(VGS-VT)因此,不考虑阈值电压的影响,饱和源-漏电流通常具有负温度系数。所以,一般MOSFET具有一定的自我保护功能,可直接并联多个联多个管芯,不会因电流分配不均匀而失效;这种并联管芯可以很容易地达到增加设备输出电流的目的(事实上,功率MOSFET采取这种措施实现大电流)。

8、为什么MOSFET饱和区跨导大于线性区跨导?

饱和区和线性区都有沟道,但根本区别在于沟道是否被夹住。电压对沟宽的影响是:栅极电压会均匀地改变沟长,源泄漏电压会不均匀地改变沟长(首先会导致泄漏极端夹)。

在线性区域,由于源泄漏电压较低,整个通道的长度从头到尾变化不大。此时,栅极电压控制通道的导电性相对较差,因此跨导率较小。同时,随着源泄漏电压的增加和通道长度的变化,通道长度减小,通过栅极电压控制通道导电的能力增强,跨导率增加。

在饱和区域,源泄漏电压较高,通道断裂,即泄漏极端的通道长度为0,因此网格电压控制通道导电的能力很强(小网格电压可以控制通道的导电和截止日期),因此跨导非常大。因此,饱和区域的跨导率大于线性区域的跨导率。

可以看出,沟越接近断裂,格栅极的控制能力越强,导线越大;沟完全断裂后,电流饱和,导线达到最大饱和导线。(饱和区域断裂,有效长度降低,线性区域无断裂,因此gm饱和区较大)

9、为什么MOSFET饱和跨导通常与饱和电压成正比?但为什么有时会与饱和电压成反比呢?

①在源-漏电压VDS一定时:由E-MOSFET的饱和电流IDsat可获得饱和跨导电压的微分gmsat与饱和电压(VGS-VT)成正比: 这种正比关系的得来,是由于饱和电压越高,就意味着沟道越不容易夹断,则导电沟道厚度必然较大,因此在同样栅极电压下的输出源-漏电流就越大,从而跨导也就越大。

②在饱和电流IDsat一定时间:饱和跨导gmsat但饱和电压(VGS-VT)成反比: 这是因为饱和电压越高,沟道越难断裂,栅极的控制能力越小,即跨导越小。

总之,饱和跨导与饱和电压成正比,而饱和跨导与饱和电压成正比。这种相反的比例关系也存在于其他场合,如功耗P与电阻R的关系:当电流确定时,功耗与电阻成正比(P=IV=I2R);当电压一定时,功耗与电阻成反比(P=IV=V2/R)。

10、为什么MOSFET线性区源-漏电导等于饱和区的跨导(栅极跨导)

MOSFET线性区源-漏电导gdlin栅极跨导在饱和区域gmsat,它们都是表示电压对沟导电的性能参数,即对源-漏电流控制能力。

在线性区时,沟道未夹断,但源-漏电压将使沟道宽度不均匀;这时源-漏电压的变化,源-漏电导gdlin也就是说,它表示了通过沟宽度的不均匀变化,在没有断裂的情况下,源-漏电压对源-漏电流的控制能力。

饱和区的栅极跨导-饱和跨导gmsat它表示了网格源电压对源泄漏电流的控制能力。此时,剩余沟的宽度不均匀,这种控制也相当于通过沟宽度的不均匀变化而起作用。因此,此时的网格极跨导相当于线性区域源泄漏导:

11、为什么在MOSFET在格栅-泄漏转移特性方面,随着格栅-源电压的增加,饱和区电流首先出现,然后线性区电流(我不明白)

E-MOSFET格栅泄漏转移特性如图1所示。格栅-源电压VGS小于阈值电压Vth设备截止日期(无通道),源-漏电流电流很小(称为亚阈电流)。

在VGS>Vth有沟,但如果源-漏电压VDS=0,不会产生电流;只有在VGS>Vth和VDS>0时,电流将产生,此时必须有VDS >(VGS-Vth),因此MOSFET在沟夹的饱和状态下,源-漏电流随着栅-源电压平方上升。由于饱和跨导和饱和电压,饱和跨导随栅-源电压线性增加。(VGS-Vth)成正比的原因。

当栅-源电压进一步增大时,使VDS

12、为什么MOSFET电流放大系数的截止频率fT与跨导gm成正比?

MOSFET的fT也就是说,输出电流随着频率的增加而下降到等于输入电流的频率。设备的跨导gm越大,输出的电流就越大,则输出电流随频率的下降也就越慢,从而截止频率就越大,即fT与gm有正比关系fT与gm成正比关系fT与饱和电压(VGS-Vth)也有正比关系,因此高频需要更大的饱和电压。

3、为什么提高MOSFET的频率与提高增益之间存在着矛盾?

MOSFET的高频率要求它具有较大的跨导,而在源-漏电压一定的情况下,较大的跨导又要求它具有较大的饱和电压(VGS-Vth),所以高频率也就要求有较大的饱和电压。因为MOSFET的电压增益是在源-漏电流一定的情况下、输出电压VDS对栅-源电压VGS的微分,则饱和状态的电压增益Kvsat将要求器件具有较小的饱和电压(VGS-VT): 这是由于在IDsat一定时,饱和电压越低,饱和跨导就越大,故Kvsat也就越大。

可见,提高频率与增大电压增益,在对于器件饱和电压的要求上存在着矛盾。因此,在工作电流IDsat一定时,为了提高电压增益,就应该减小(VGS-VT)和增大沟道长度L。这种考虑对于高增益MOSFET具有重要的意义;但是这种减小(VGS-VT)的考虑却对于提高截止频率不利。

14、为什么E-MOSFET的栅-源短接而构成的MOS二极管存在着“阈值损失”?

这种集成MOS二极管的连接方式及其伏安特性。因为栅极与漏极短接,则VGS=VDS。因此,当电压较小(VGS=VDS(VGS-VT)关系,于是出现了沟道、但总是被夹断的,所以器件处于饱和状态,输出源-漏电流最大、并且饱和,为恒流源。

由于VGS=VDS,所以这种二极管的输出伏安特性将与转移特性完全一致。因为MOSFET的饱和输出电流IDsat与饱和电压(VGS-VT)之间有平方关系,所以该二极管在VGS=VDS≥VT时的输出伏安特性为抛物线关系,并且这也就是其转移特性的关系。

所谓阈值损失,例如在门电路中,是输出高电平要比电源电压低一个阈值电压大小的一种现象。由E型,栅-漏短接的MOS二极管的伏安特性可以见到,当其输出源-漏电流IDS降低到0时,其源-漏电压VDS也相应地降低到VT。这就意味着,这种二极管的输出电压最低只能下降到VT,而不能降低到0。这种“有电压、而没有电流”的性质,对于用作为有源负载的这种集成MOS二极管而言,就必将会造成阈值损失。

15、为什么在MOSFET中存在有BJT的作用?这种作用有何危害?

①对于常规的MOSFET:如图3(a)所示,源区、漏区和p衬底即构成了一个npn寄生晶体管。当沟道中的电场较强时,在夹断区附近的电子即将获得很大的能量而成为热电子,然后这些热电子通过与价电子的碰撞、电离,就会形成一股流向衬底的空穴电流Ib;该过衬底电流就是寄生晶体管的基极电流,在热电子效应较严重、衬底电流较大时,即可使寄生晶体管导通,从而破坏了MOSFET的性能。这种热电子效应的不良影响往往是较短沟道MOSFET的一种重要失效机理。

②对于CMOS器件:在CMOS器件的芯片中,存在着npnp的四层结构——晶闸管。当其中的BJT因为热电子效应而导通时,即可发生所谓“闩锁效应”、而导致器件失效。

③对于VDMOSFET:观察图3(b)中的结构,即可见到,当器件正向导通时,其中存在一个工作于放大状态的寄生n-p-n晶体管(n+源区是发射区,n-外延层是集电区,p沟道是基区)。该寄生晶体管的可能导电通道是与MOSFET的ID相并联的,故在VDMOSFET工作时,必须要注意防止寄生晶体管导通;否则,寄生晶体管的导通就可能引起二次击穿,使得功率MOSFET完全失去功能。

为了避免VDMOSFET在正向工作时、其中寄生n-p-n晶体管的导通,可以设法使寄生晶体管的电流放大系数变得很小、甚至减至为0——采用“阴极短路技术”,即把寄生晶体管的发射极与基极短接起来,工艺上就通过把发射区(源极区)的金属电极延伸到沟道体区的表面上来实现。因为这种阴极短路结构截断了发射极注入载流子的功能,所以能够防止寄生晶体管的导通。

对于VDMOSFET,在采用了阴极短路结构之后,实际上又恰恰在器件内部形成了一个p-n-n+二极管,这个二极管与VDMOSFET是反向并联的,这也就顺便地在VDMOSFET中设置了一个阻尼二极管(续流二极管),该二极管对于泄放反向电动势、防止主体晶体管的击穿具有重要作用。

16、为什么在VDMOSFET中存在有JFET的作用?有何不良影响?

源-漏电流是从芯片表面向下流动的,并在电流通路的两侧是pn结,因此这种电流输运的过程,从工作原理上来看,就相当于是一个寄生JFET。从而可以把VDMOSFET等效为一个MOSFET与一个寄生JFET的串联组合,其中很大部分n-漂移区就相当于是寄生JFET的沟道。

由于JFET的输出交流电阻非常大,同时也因为较高的源-漏电压而具有很大的输出直流电阻,所以就使得VDMOSFET的导通电阻大大增加,因此n-漂移区的厚度和掺杂浓度对整个器件性能的影响都较大。

为了消除VDMOSFET中寄生JFET的影响,以降低导通电阻,就必须在结构上加以改变,由此发展出了V形槽栅、U形槽栅和沟槽(Trench)栅等结构的MOSFET。

17、IGBT和MCT都是MOS栅极控制的功率场效应晶体管,为什么说它们是两种完全不同的器件?

IGBT(绝缘栅双极型场效应晶体管)和MCT(MOS控制晶闸管)的共同点主要有:

①都是MOS栅极控制的器件,则具有功率场效应晶体管的优点;

②在结构上,其中都存在着四层、三结的晶闸管结构,因此在一定条件下会出现阳极电流闩锁效应;

③它们都可以采用多个元胞并联的结构,因此可以获得很大的工作电流;

③它们都是有两种载流子参与工作的器件,因此都是双极型的场效应晶体管,导通电阻低,但开关速度也相对地要比MOSFET的低。

IGBT和MCT的最大不同点就在于它们的工作状态和性质不相同,因此说它们是两种完全不同的器件:

①IGBT的工作电流主要是通过MOS沟道的电流,而其中的晶闸管电流是需要极力避免的(IGBT的最大工作电流——擎住电流就是其中晶闸管不导通时的电流),因此从本质上来看,IGBT基本上是一种MOSFET,因此IGBT具有MOS器件的许多优点,例如较强的栅极的控制能力和较低的驱动功率(因为有很大的输入电阻和较小的输入电容之故)。

而MCT与IGBT的恰恰相反,它的工作电流主要是晶闸管电流,至于MOS沟道的电流,则主要是起着触发晶闸管导通或者关断的作用,不是MCT的主要工作电流,因此从本质上来看,MCT基本上是一种晶闸管——双极型器件,从而MCT具有导通电阻很低、耐压很高、功率容量很大的优点。

②IGBT虽然在本质上是一种MOS器件,但又不同于一般的MOSFET,因为IGBT在导通工作时,有少数载流子注入到高阻的耐压层(漂移区),可以产生电导调制,则它的导通电阻较小,增大了器件的电流容量(电流密度要比VDMOSFET的高2~3倍);同时由于高阻耐压层的引入而提高了工作电压。因此IGBT的功率容量很大。只是IGBT的开关速度,由于少数载流子的引入而相应地有所降低。

③虽然MCT本质上是一种晶闸管,而且MOS栅极可以关断阳极电流,但MCT又不同于一般的可关断晶闸管(GTO)。因为MCT实际上是一种把单极型的MOSFET与双极型的晶闸管组合而成的复合型器件,也是一种所谓Bi-MOS器件,所以它具有MOS器件和双极型器件二者的长处:较强的栅极控制能力,较低的驱动功率,较高的开关速度,较大功率容量。

16、电流镜中如何减小阈值电压失配,以及跨导参数失配(Kp=μCox)?

提高过驱动电压,可以减小阈值电压失配,提高跨导参数可以减小跨导参数失配(CMOS尺寸减小,tox减小,Cox增大)

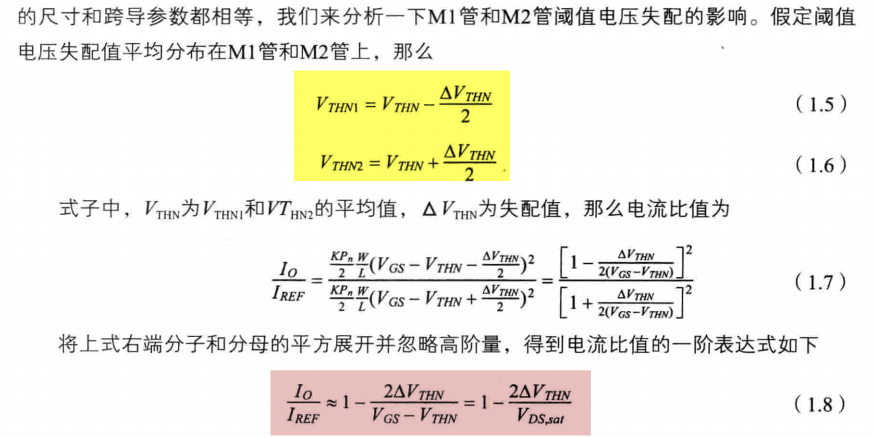

阈值电压失配:

定量分析:

定性分析:电流镜电流一定的情况下,阈值电压失配出现在过驱动电压里,为了减小阈值电压在过驱动电压中的影响,可以减小阈值电压在过驱动电压中的占比,增大Vgs即增大过驱动电压,而减小W/L。

跨导参数失配Kp(μCox)

定量分析:

定性分析:CMOS尺寸减小,栅氧化层厚度减小tox,因此Cox增大即Kp增大

17、对于折叠式共源共栅放大器,Vos主要是哪几个产生的?

对于共源共栅放大器,忽略共源放大器的沟道长度调制效应,从噪声电流考虑,共栅放大器,Id+In=0,没有噪声电流经过输出。从噪声电压考虑,Vn在共栅的栅极到输出端的Vout等于等效于带源极负反馈的共源放大器:Av=gmRd/1+gmRs,,Rs较大,因此共栅的噪声电压可以忽略不计;对于共源放大器,从噪声电压考虑,输入到输出,相当于带负载的共源放大器:Av=gmRd,因此共源放大器的噪声不能忽略。

18、画出在Nwell中的PNP