[收藏] Flash闪存颗粒和工艺知识深度解析

时间:2023-01-10 19:30:00

转载:[收藏] Flash闪存颗粒和工艺知识深度分析

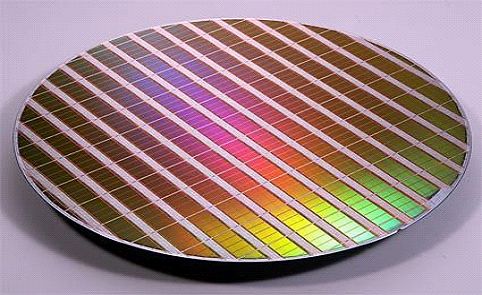

Wafer也就是说,晶圆是一种高纯度硅晶体柱,由半导体组件晶片或芯片的基材高温拉伸而成(Crystal Ingot)切下来的圆片叫晶圆。通过感光工艺获得所需的光阻,然后对硅材料进行精密蚀刻槽,继续用金属真空蒸煮工艺,从而在各自独立的晶粒中(Die)完成各种微组件和微线。晶圆背面需要另行蒸上金层作为晶粒固定(Die Attach)用于脚架。

上述流程称为Wafer Fabrication。早期在小集成电路时代,每一个6寸的晶圆上制作数以千计的晶粒,现在次微米线宽的大型VLSI,每8寸晶圆只能完成一两百个大芯片。我们NAND Flash的Wafer,目前主要使用8寸和12寸晶圆,一个晶圆只能做一两百个NAND Flash芯片来。

NAND Flash Wafer

Wafer虽然制造业经常投资数百亿,但它是所有电子工业的基础。晶圆的原料是硅,地壳表面有用的二氧化硅。二氧化硅矿石经电弧炉提炼,盐酸氯化,蒸馏后制成高纯度多晶硅,纯度高达99.99%以上。晶圆制造商将这种多晶硅熔化,然后在溶液中种植籽晶,然后慢慢拉出形成圆柱形单晶硅晶棒,因为硅晶棒是在熔融硅原料中逐渐生成的晶体表面确定的晶体,这个过程被称为长晶体。硅晶棒经过切割、研磨、切割、倒角、抛光、激光雕刻、包装后,成为集成电路工厂的基本原料——硅晶片,即晶片。

下图是NAND Flash简单的生产流程:

Die芯片封装前的晶粒来自硅晶圆(Wafer)激光切割的小片(Die)。每一个Die它是一种独立的功能芯片,由无数的晶体管电路组成,但最终会被封装成我们常见的闪存颗粒,CPU常见芯片等。

什么是ink Die

在晶圆制造过程中,会对Wafer中的每个Die严格测试,通过测试Die,就是Good Die,未通过测试的即为Ink Die。测试过程完成后,会有一个Mapping图,在Mapping不良的内部会用颜色标记Die,故称Ink Die。

Flash芯片包装分类

目前NAND Flash多采用封装方式TSOP、FBGA与LGA其他方法,由于终端电子产品转向轻、短趋势,因此减少体积和低成本的包装方法已成为NAND Flash封装发展的主流趋势。

TSOP:(Thin smaller outline package)目前封装技术应用最广泛NAND Flash包装技术,首先在芯片周围引脚,采用SMT直接附着在技术(表面安装技术)上PCB板的表面。TSOP在包装过程中,寄生参数减少,适用于高频相关应用,操作方便,可靠性高,成品率高,价格低廉,因此得到了广泛的应用。

BGA:(Ball Grid Array又称锡球数组包装或锡脚包装)包装方式,主要用于计算机内存、主板芯片组等大型集成电路的包装领域,FBGA封装技术的特点是,虽然导线数量增加,但导线间距不小,因此提高了组装率。虽然功率增加,但FBGA能大大提高电热性能,减轻重量,顺利传输信号,提高可靠性。

采用FBGA新技术包装的内存可以在体积不变的情况下,将所有计算机中的内存容量提高数倍TSOP体积小,散热性能好,FBGA封装技术大大提高了每平方英寸的储存量,体积却只有TSOP三分之一的包装与传统包装TSOP封装模式相比,FBGA加快传输速度,提供有效的散热方式,FBGA除了优异的电气性能和散热效果外,封装还提供了优异的内存稳定性和更多未来应用的扩展性。

LGA:(Land Grid Array)接触显示包装,即在底部制作几组状态坦电极接触包装,组装插入插座,现有227触点(1.27mm中心距)和447触点(2.54mm陶瓷中心距)LGA,用于高速逻辑LSI电路,由于引线的阻电抗小,对高速LSI但由于插座制作复杂,成本高,普及率低,未来需求可能会逐渐增加。

Flash芯片封装叠Die(Stack Die)

由于NAND Flash单颗Die容量有限。为了实现更高的容量,需要在一个包装片中堆叠几个Die。在Wire Bond用金线互连。

目前单颗Die容量最高的是Micron公司的MLC 4GB,目前最先进的堆叠技术可以堆叠8层,所以理论上MLC单个封装件可实现32个GB。Micron公司计划在09年Q推出此容量的封装片。

Flash芯片TSOP封装和BGA封装内部结构

TSOP包装只需要一个引脚框架NAND FLASH Die的Pad打线(Wire Bond)连接到引进框架上。包装技术简单,成本低。但是它的打线方式只能从两边打线,所以stack die更难。

BGA封装与TSOP不同的是,它采用了包装Substrate,用电路板引脚走线,所以可以四面打线,这样就可以叠了die它变得更容易操作。但成本会比成本更高TSOP要高。

Flash芯片包装尺寸,部分包装尺寸比较:

NAND Flash出货有两种产品样式:

一种是Wafer,即晶圆出货,这种产品样式一般客户采购回去需要再测试和COB封装等,这种客户多为闪存卡大客户。

一种是封装片出货,NAND Flash目前最普遍采用的是48TSOP1的封装方式,现货市场均为TSOP的封装片。

NAND Flash按工艺可分为SLC与MLC

SLC英文全称(Single Level Cell)即单层式单元储存。SLC技术特点是在浮置闸极与源极之中的氧化薄膜更薄,在写入数据时通过对浮置闸极的电荷加电压,然后透过源极,即可将所储存的电荷消除,通过这样的方式,便可储存1个信息单元,这种技术能提供快速的程序编程与读取,不过此技术受限于Silicon efficiency的问题,必须要用较先进的流程强化技术,才能向上提升SLC制程技术。

MLC英文全称(Multi Level Cell)即多层式单元储存。Intel在1997年9月最先开发成功MLC,其作用是将两个单位的信息存入一个Floating Gate(闪存存储单元中存放电荷的部分),然后利用不同电位(Level)的电荷,通过内存储存的电压控制精准读写。MLC通过使用大量的电压等级,每一个单元储存两位数据,数据密度比较大。SLC架构是0和1两个值,而MLC架构可以一次储存4个以上的值。因此,MLC架构可以有比较高的储存密度。

TLC英文全称(Triple Level Cell)即一个单元可以存储单元可以存储3bit,因此需要8个等级的电位进行编码解码才能实现。其实TLC是属于MLC的一种。

SLC和MLC的基本特性表

Flash坏块的形成

NAND Flash的存储原理是,在写入(Program)的时候利用F-N隧道效应(Tunnel Injection隧道注入)的方法使浮栅充电,即注入电荷;在擦除(Erase)的时候也是是利用F-N隧道效应(Tunnel Release隧道释放)将浮栅上的电荷释放。

隧道注入和隧道释放的产生都需要十几伏的瞬间高电压条件,这对浮栅上下的氧化层会造成一定损伤,因此这样重复的操作(P/E Cycle)是有限的。SLC大概是100K次,MLC大概是10K次。达到读写寿命极限的时候存储单元就会出现失效,然后就会造成数据块擦除失效,以及写入失效,于是就会被标记起来,作为坏块,并将这个标记信息存放在Spare Area里面,后续操作这个Block时,需要Check一下这个信息。

Flash固有坏块

由于制造工艺的原因,通常普通的NAND FLASH从出厂开始就有坏块了,一般在2‰以下。一般芯片原厂都会在出厂时都会将坏块第一个page的spare area的第6个byte标记为不等于0xff的值。

NAND Flash的存储单元是有使用寿命的

NAND Flash的存储原理是,在写入(Program)的时候利用F-N隧道效应(Tunnel Injection隧道注入)的方法使浮栅充电,即注入电荷;在擦除(Erase)的时候也是是利用F-N隧道效应(Tunnel Release隧道释放)将浮栅上的电荷释放。隧道注入和隧道释放的产生都需要20V左右瞬间高电压条件,这对浮栅上下的氧化层会造成一定损伤,因此这样重复的操作(P/E Cycle)是有限的。SLC大概是100K次,MLC大概是10K次。

三星估算的SSD硬盘的寿命

如果每天对SSD写入4.8GB的数据,假设SSD总容量为16GB,那么,你至少需要3.34天才能对整个SSD的每个单元擦写一次;如果此SSD为擦写次数为100K的SLC单元,那么,你至少需要3.34×100K天才能使这个SSD完全失效;3.34×100K天=913年,因此16G的SSD可以使用913年。那么,如果是MLC的话,也至少可以使用91.3年。

晶圆制程工艺发展历史

芯片制程工艺是指晶圆内部晶体管之间的连线间距。按技术述语来说,也就是指芯片上最基本功能单元门电路和门电路间连线的宽度。

主流厂商的晶圆制程工艺以及下一代制程工艺的情况,如下表。

芯片制造工艺在1995年以后,从0.5微米、0.35微米、0.25微米、0.18微米、0.15微米、0.13微米、90纳米、75纳米、65纳米一直发展到目前最新的34纳米。

一步步印证了摩尔定律的神奇。以90纳米制造工艺为例,此时门电路间的连线宽度为90纳米。我们知道,1微米相当于1/60头发丝大小,经过计算我们可以算出,0.045微米(45纳米)相当于1/1333头发丝大小。可别小看这1/1333头发丝大小,这微小的连线宽度决定了芯片的实际性能,芯片生产厂商为此不遗余力地减小晶体管间的连线宽度,以提高在单位面积上所集成的晶体管数量。采用34纳米制造工艺之后,与65纳米工艺相比,绝对不是简单地令连线宽度减少了31纳米,而是芯片制造工艺上的一个质的飞跃。

目前最先实现34nm工艺的是Intel和Micron联合投资的IM,此技术被最先应用在了NAND FLASH上面,可见NAND FLASH的制程工艺跳跃是所有IC中最快的。

晶圆技术的发展都是受生产力驱动,必须向更小的制程间距和更大的晶圆尺寸发展。制程从2.0um、0.5um、0.18um、90nm一直到目前的34nm,晶圆尺寸从最初的5英寸发展到目前的12英寸,每次更迭都是一次巨大的技术跳跃,凝聚了人类科技的结晶,也一次次印证了摩尔定律的神奇。

晶圆尺寸的大约每9年切换一次。而晶圆制程由最初的几年更迭一次,到目前的基本上每年都能更迭一次。