小刘同学的CMOS模拟集成电路学习小记(不停更新)

时间:2023-01-08 00:30:00

从今天开始,我们来看看拉扎维的模拟集成电路设计,希望能得到更多的感受。

PS:这篇文章不是为新手学习而建立的,而是为了总结我在再次阅读时没有深入理解的概念。不断回顾,发现一个新问题或以前没有注意到的概念,并不断更新。

与君共勉。(有问题可以留言,一起讨论)

以下目录:

CMOS模拟集成电路设计

- 第二章 MOS器件物理基础

- 第三章 单极放大器

- 第四章 差动放大器

- 第五章 电流镜和偏置技术

- 第六章 放大器的频率特性

- 第七章 噪声

- 第八章 反馈

- 第九章 运算放大器

- 第十章 稳定性和频率特性

- 第十一章 纳米设计分析

- 第十二章 带隙基准

- 补充内容 virtuoso模拟电路记录

第二章 MOS器件物理基础

1、2021年11月23日:

“关于nmos当衬底电压低于源极电压时,阈值电压会变高。p衬底中的空穴被赶出栅区,留下负离子形成耗尽层。界面电势足够高后,形成反向层。此时,电压Vg称为阈值电压。需要注意的是,p衬底是空穴为多子,Vg上升就是赶空穴留电子,而不是吸引电子来中和空穴。因此,当衬底电压低于源极电压时,会吸引空穴排斥电子,使栅区耗尽层变大,相当于Vg排斥空穴的能力变弱,需要Vth变大。

书P30,“Vsb增加,身体效应减弱。gmVgs与gmbVbs具有相同的极性,即增加格栅压力与增加衬底电压相同。体效应是指Vb下降,Vth增加(Vs=Vd=0,Vg略小于Vth在没有反形层的情况下,使栅下有耗尽层)。为了增加漏极电流,增加了栅压。增加衬底电压,Vbs变大,gmb也变大,等效vbs*gmb漏极电流也变大了。Vsb增加,身体效应减弱,还有一些反应。

第三章 单极放大器

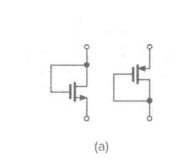

1.2021年11月24日,书P56.互补共源级和电流源负载共源级感觉有点重要。在这里留言。特别是在互补共源级中,两个晶体管的偏置电流是PVT两管的阈值电压直接构成强函数VDD,VDD或者当阈值电压发生变化时,。互补共源级也会放大VDD噪声(习题3.31)。以后越学会关注各种外部条件的变化给电路带来的变化,这也是模电的形而上学。各种变化总是联动的,必须从小就积累知识点。

2、2021年12月18日,书P79.在给定偏置电流的条件下,有两种方法可以改善输出阻抗:共源共栅结构和增加L。对于后者,是因为晶体管的本增增益为gm * ro。ro=1/(lamda * Id)。lamda正比于1/L。故ro约为L/Id。

3.2022年4月21日。这一次,我想谈谈我在二极管连接型共源极中总是犯的逻辑错误(两次,我很生气):

二极管连接型nmos,Vds=Vgs,Vds>=Vgs-Vth泄漏电流大时永成立(漏电流太小,管道进入亚阈值区)。人们喜欢把Vov代替Vgs-Vth,总喜欢在计算中使用Vds,min>=Vov。好了,问题来了,用多了就老了。Vds当作Vov算了吧,形成了逻辑惯性。

二极管连接型:

Vds=Vgs => Vds=Vov Vth。

重要的话说三遍:

二极管连接型时,Vds=Vov Vth。

二极管连接型时,Vds=Vov Vth。

二极管连接型时,Vds=Vov Vth。

以下是一个用例:

上一个例子是《模拟集成电路与系统》196页的用例。有了我的逻辑惯性,风格(5-42)会很尴尬。我总是把它放在一边Vov当成此时的Vds。专门在这里发,加深印象。

以这个例子为例,我还是趁热打铁放这个高级版的电路,就是觉得这个电路把计算用到了极致,不禁让我扣666。

I0=1/2K(W1/L1)Vov6 * Vov6

2I0=2/3K(W1/L1)[(Vx Vov6 Vth)-Vth-1/2Vx]Vx

得出:3Vov6 * Vov6 - 2Vov6Vx - Vx * Vx=0

所以:Vx=Vov6 => Vb=Vx Vgs7=Vov6 Vov7 Vth。

都想为作者鼓掌。

第四章 差动放大器

1.2022年1月6日,书上112页CMRR的计算,之前没有把差模增益算出来,这回进行了计算:

第五章 电流镜和偏置技术

1.2022年1月6日。关于共源共栅电流镜两种使Vds一种相等方法的想法。Vds1=Vgs1=Vgs2。Vds2>=Vgs2-Vth在饱和区工作。在书的127页,图5.12,上有X,Y点,X点是M1的漏区,Y点是M2的漏区。若不做任何处理,且右侧刚好满足漏源电压等于过驱动电压,X点电压高于Y点电压Vth的。所以有两种方法可以平衡,第一种是提高右Y点电压Vth,成本是电压余度低Vth,二是左侧X点下降Vth,就像书中使用电阻降压一样,满足电阻上的压降Vth,成本是电阻会引入热噪声或影响电路速度(这两个我自己拉的,应该有,错了可以纠正。)

2、2022年1月6日,这部分最重要的就是五管OTA算了吧,第一次看的时候还是没好好看书,原来电子版的第二版拉扎维这里都有印刷错误:

公式(5.27)多出来一个2。书这部分的内容也有很多错误,比如节点X,F,Y傻傻分不清楚。原来别人的正版书都没有错误。前天,下单了一本正版书,看来这个钱是省不下了。

第六章 放大器的频率特性

2022.4.10

需要注意源跟随器的输入阻抗的负阻效应与输出阻抗的感性,比较特殊。

第七章 噪声

2022.4.10

这部分没什么坑。

第八章 反馈

2022.4.10

1、反馈部分的一部分总结:

按反馈网络的输入输出端来讲,输入端检测电压就要并联,并联就要降低电阻,检测电流就要串联,串联就要增加电阻;输出端输出电压就要串联,串联就要增加电阻,输出电流就要并联,并联就要降低电阻。

2、之前一直忽略了加载效应(一算那些公式就想睡觉)这里补回来了:

加载效应用到了二端口网络模型,一共四种网络模型。如何确定前馈网络与反馈网络使用哪种模型呢?就看那个X21(这里的X泛指Z,Y、H、G)。比如前馈网络是电阻型,那只有Z21符合,剩下的类比使用。选定好网络后,加载部分一般是{z11 z22}{y11 y22}{h11 h22}{g11 g22}。快速写一下公式或者心里想一下,就知道反馈端短路还是开路了。需要注意的是反馈与前馈的输入输出是反着的,不要搞混了。

第九章 运算放大器

2022.3.1

发现一个我一直忽略的逻辑错误!!!nmos构成电阻负载共源极,漏电流上升时,由于电阻压差增加,漏端电压下降;pmos构成的电阻负载共源极,漏电流上升,电阻压差增加,漏端电压上升。因为一个相对于地,一个相对于电源电压。这么简单的错误,今天才发现,我就说我看图9.54下面的话总觉得别扭,原来我一直没考虑过pmos的情况!(实属不该)

第十章 稳定性与频率特性

第十一章 纳米设计分析

2022.4.10

文章上来就是深亚微米效应,速度饱和与纵向电场导致的迁移率退化,这个非常重要,不过知道结论就行了,仿真的时候特别明显,各种参数飘来飘去全拜这些二级效应所赐。

第十二章 带隙基准

正在看。

补充内容 virtuoso电路仿真记录

给我别的帖子来引个流,嘿嘿。

小刘同学的模拟IC仿真记录(初学virtuoso ic 618)