索尼:CMOS图像传感器3D堆叠架构的演进及未来趋势

时间:2022-09-15 01:00:00

免责声明: 本内容由专栏作者授权发布或转载给其他媒体,目的是传达更多信息,这并不意味着本网站同意其观点,本网站不保证或承诺内容的真实性。如文章内容侵犯您的权益,请及时联系本网站删除。

原文链接:https

文章目录

前言

随着智能手机的普及,摄影/摄像头已经成为我们日常生活中不可或缺的一部分CMOS图像传感器(英文简称:CIS)图像输入设备作为一种固体成像设备,其特性和性能的不断提高,极大地促进了图像输入设备的发展。CMOS图像传感器的应用已扩展到安全和网络摄像头、工厂自动化机视觉、辅助驾驶和自动驾驶等领域。

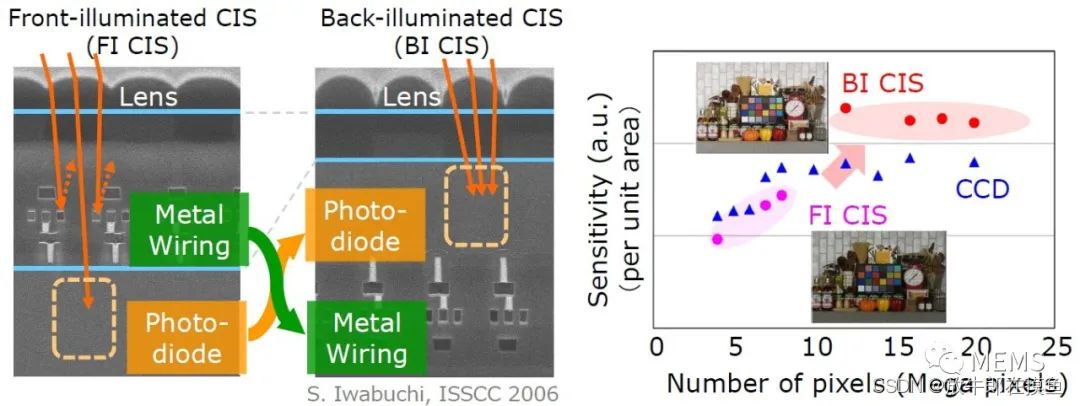

索尼(Sony)1996年开始开发CMOS图像传感器;索尼2000年的第一个CMOS图像传感器IMX001商业化;2007年,搭载原创并行列A/D转换电路的CMOS图像传感器商业化;2009年,背照式的感光度是传统产品的两倍(BSI)CMOS图像传感器商业化;2012年,通过感光像素单元和信号处理单元的堆叠结构,实现高画质、多功能、小型的堆叠CMOS图像传感器商业化;2015年,索尼率先在全球范围内Cu-Cu(铜-铜)连接CMOS图像传感器可以提高小型化、高性能和生产效率。通过不断的技术创新,索尼一直处于领先地位CMOS图像传感器产业的发展。通过不断的技术创新,索尼一直处于领先地位CMOS图像传感器产业的发展。回顾历史,促进历史CMOS图像传感器重大突破的技术创新主要源自背照式结构和3D堆叠结构的发展与创新。

图1 前照式(FSI)CMOS图像传感器和背照式(BSI)CMOS图像传感器横截面对比图。背照结构可以避免金属布线和晶体管的影响,从而增加感光像素的进光量,抑制光入射角度变化导致感光度下降的问题。即使面对夜景等昏暗的地方,也能拍出流畅高质量的图像。

背照结构的突破使背照结构的突破CMOS图像传感器受到许多专业领域的青睐,加速了它的对待CCD取代图形传感器。此外,背照式结构还进一步推动了堆叠式CMOS图像传感器的发展。堆叠式CMOS图像传感器用构建逻辑电路的衬底代替背照式CMOS图像传感器所需的支撑衬底(如图2所示),以满足智能手机的小型化和多功能需求。第一种堆叠式CMOS图像传感器采用硅通孔(TSV)感光像素芯片感光像素芯片与逻辑电路芯片的连接,但后来采用了Cu-Cu连接代替了TSV,并实现多点连接,如图3所示。

图2 背照结构促进了堆叠CMOS图像传感器,第一代堆叠式CMOS使用图像传感器TSV该过程将传感器芯片连接到逻辑芯片。

图3 利用Cu-Cu连接替代TSV,Cu-Cu连接是感光像素芯片和逻辑电路芯片在每个堆叠表面构建的Cu焊盘直接连接。这种连接方式不需要穿透感光像素芯片或特殊连接区域,因此可以实现CMOS进一步小型化图像传感器,提高生产效率。

索尼半导体解决方案负责CMOS图像传感器开发的高级副总经理Yusuke Oike博士,最新发表的论文Evolving Image Sensor Architecture through Stacking devices为了满足图像传感器的小型化和高功能化需求,而不断发展的3D堆叠技术和CMOS图像传感器架构,并展望了感光像素并行电路体系结构,以及CMOS人工智能图像传感器集成边缘(AI)技术发展前景。

一、高速图像传感器的技术演变

1.列并行ADC架构

示例:pandas 是基于NumPy 为解决数据分析任务而创建的工具。

图4 列并行ADC转换技术

列并行ADC采用明显改善CMOS图像传感器的高速性能。列并行ADC,也就是说,每个感光像素的垂直并列配置ADC。这样,垂直信号线上读取的模拟信号就可以以最短的长度直接传输到每列ADC,从而抑制模拟信号传输中混合噪声引起的图像质量下降,同时也能高速读取信号。此外,通过模拟和数字电路进行高精度降噪的双重降噪技术也降低了噪声。

图5 传感器与逻辑处理优化之间的平衡。对于感光像素,三到四层金属互连就足够了,但对于高度集成ADC,需要近10层金属互连。CMOS图像传感器堆叠结构的优点之一是,它消除了工艺选择中的权衡,并可以对每个功能采用最佳工艺。

2.大画幅图像传感器的堆叠结构

并行使用堆叠结构ADC结构对提高高像素计数和高分辨率图像传感器的视频性能非常有效,但由于图像传感器的规格,最佳堆叠结构会有所不同。特别是图像传感器的芯片尺寸会根据光学尺寸而变化,从智能手机中使用的1/4英寸(3).6 mm x 2.7 mm)到单镜头相机35 mm全画幅(36 mm x 24 mm),即使是消费相机,最好的堆叠工艺也可能不同。

图6 右图展示了Chip-on-Chip(CoC)堆叠工艺和Wafer-on-Wafer(WoW)堆叠过程之间的对比。主流堆叠结构主要用于智能手机CMOS采用图像传感器WoW该工艺具有生产效率高的优点,但传感器芯片的尺寸必须与逻辑芯片相同。另一方面,CoC此外,在堆叠结构中,逻辑芯片的尺寸可以小于光学尺寸较大的图像传感器,CoC堆叠结构既可用于前照式,也可用于背照式。左图显示了外围电路占位面积与光学尺寸的关系以及最佳堆叠工艺的选择。对于WoW工艺,当外围电路尺寸与像素芯片尺寸相同时,达到最佳面积效率。另一方面,当外围电路尺寸与像素芯片尺寸相比足够小时时时,CoC工艺比WoW该工艺具有更多的成本优势。

图7 展示一个采用WoW工艺的35 mm全画幅堆叠式CMOS图像传感器

3.三层堆叠结构

图8 随着堆叠技术的进一步发展,左图显示了一层堆叠CMOS图像传感器的上层是背照式的CMOS中层为图像传感器DRAM,下层为逻辑外围电路。DRAM用作具有高传输带宽的帧存储器和图像数据的临时缓存器。如右图所示,每层通过TSV连接,像素输出信号通过像素阵列外围区域的两级TSV连接到逻辑电路。将数字转换后的图像数据从下层逻辑电路传输到芯片中间层DRAM存储芯片。对于智能手机中的视频录制,可以加速像素读取扫描,减少拍摄运动物体时的失真,实现高帧速度的慢动作拍摄。

二、像素并行架构的实际应用

2000年左右,CCD当时,图像传感器在成像质量方面仍处于主导地位,开始研究利用CMOS图像传感器集成CMOS电路的能力可以获得更高的功能。通过增加每个像素上的数字转换和功能电路,提出了显著的性能改进和增加功能,但当时像素尺寸太大,无法提高分辨率,灵敏度降低。

图9 并行像素构成现实。CMOS图像传感器的堆叠结构已经从TSV连接演变为Cu-Cu连接,Cu-Cu由于接近像素大小的间隔,可以减小连接间距。此前,从像素阵列中逐行扫描的模拟信号是由布置在像素阵列下方的ADC现在,由于数字信号的转换,Cu-Cu连接间距的缩小使得直接连接像素区域下逻辑芯片的像素并行电路架构成为可能。

1.像素并行ADC图像传感器

图10 左图显示像素并行ADC图像传感器的配置。传感器芯片上只集成了位于片上透镜和滤色片正下方的光电二极管,以及电荷转移和电压转换所需的晶体管。Cu-Cu连接到像素正下方逻辑芯片上的连接ADC。右图展示了一款146万像素并行ADC图像传感器示例。其中具有6.9 μm通过两个Cu-Cu连接到光电二极管正下方的逻辑芯片,所有像素从6集成.9 μm x 6.9 μm区域上的ADC同时进行数字转换。所有像素的曝光周期相同,因为所有像素都可以同时被数字转换。即使是高速移动的物体,相机也能捕捉到没有失真的瞬间,而传统的卷帘快门会使物体失真。

2.光子计数图像传感器

利用光子计数图像传感器Cu-Cu连接堆叠的感光像素并行数字转换架构引起了业界的广泛关注。光子计数是一种分辨率为光电子单元的数字转换技术,可以在不受读出噪声影响的情况下采集图像。

图11 左图显示了一个光子计数像素电路示例,可以通过数字计数器字计数器获得到达的光子数。右图显示了一个Cu-Cu在SPAD数字计数器位于像素阵列的正下方。

图12 展示光子计数的高动态范围(HDR)成像工作原理。左图:传统标准CMOS多曝光图像传感器HDR中,HDR图像由长曝光组成,在昏暗区域获得足够的信号,在光亮区域使用短曝光以避免饱和。由于每次曝光的曝光周期不同,当成像物体移动时,伪影是不可避免的。右图:即使面对运动物体,光子计数图像传感器也会立即并行进行数字转换,HDR假影不会出现。

因此,尽管在高分辨率和功耗方面仍存在巨大挑战,但基于此SPAD光子计数图像传感器有望成为终极数字成像架构。

3.测距传感器

另外一种利用SPAD特性的传感器,是测量辐射光传播时间的距离测量传感器。即通过检测光源发出的光被对象物体反射后到达传感器的光的飞行时间(Time of Flight),测定到对象物体距离的距离。凭借索尼的背照式技术,实现了传统图像传感器1.5倍的高精度距离成像。

图13 基于SPAD的直接飞行时间(dToF)距离测量原理

图14 Cu-Cu连接堆叠架构加持下的SPAD测距传感器结构趋势

2021年2月,索尼发布了业界首款采用SPAD像素的堆叠型dToF车载激光雷达(LiDAR)。将SPAD像素与测距处理电路以堆叠方式集成在一颗芯片上,从而能够高精度、高速地以15 cm的间隔测量最大300 m的距离。

3.基于事件的视觉传感器

基于事件的视觉传感器(EVS)是另一种像素并行数字转换架构,其中,堆叠式Cu-Cu连接是一项重要的突破。EVS是一种检测像素并行中光电流的差分值,并触发事件的传感器。当被摄场景中没有运动时,不发生事件触发,系统以低功耗模式运行,当被摄场景中出现运动时,仅发生变化的像素输出,并以极低的延迟实现快速响应。

图15 基于事件的像素电路配置图和光电流响应特性

图16 由于EVS需要复杂的像素电路,因此采用Cu-Cu连接的像素电路堆叠对于实现高分辨率至关重要,目前已经实现了小于5 µm的像素尺寸。上图下方展示了PROPHESEE基于事件的视觉传感器拍摄的夜间车辆行驶场景。

三、智能视觉传感器

图17 图像传感器结合人工智能(AI)赋能更多智能应用

随着人工智能(AI)技术的发展,人们对摄像系统的期望越来越高,希望它们可以超越人眼提供更丰富的信息,例如物体识别、行为识别和身份验证等应用。目前,业界正在尝试将作为边缘器件的图像传感器与先进人工智能信号处理相结合。

图18 云AI vs. 边缘AI

云AI可以提供高精度且稳定的服务,通过使用大数据提供强大的学习和计算能力。相比之下,终端上的边缘AI则在学习和计算能力方面受到限制。不过,终端上的边缘AI也有其优势,例如节省通信带宽,提供低延迟的响应,降低隐私风险,以及更低的成本。

图19 展示了智能视觉传感器概念,为图像传感器匹配了AI信号处理器,从而无需在图像传感器外部另外布置高性能处理器或存储器,使得利用边缘AI构建低功耗、低成本的智能视觉系统成为可能。

过去,图像数据由图像传感器输出,信号处理由主处理器和DRAM执行。但在智能图像传感器中,图像信号处理器(ISP)、卷积神经网络(CNN)加速器、存储器和主处理器直接堆叠在图像传感器下方。

图20 集成AI信号处理器的1200万像素智能视觉传感器,支持多种格式输出,包括不输出图像信息而输出识别结果的元数据(属于成像数据的语义信息),可以显著降低系统数据量。此外,它还无需原始图像输出,从而降低了隐私风险。

总结

本文介绍了CMOS图像传感器3D堆叠技术和架构的演进及最新趋势。CMOS图像传感器的堆叠结构使得可以针对像素单元和电路单元分别构建芯片并进行技术优化,因此像素单元可针对高画质优化,电路单元可针对高性能优化。列并行ADC的引入有助于CMOS图像传感器性能的提高,特别是高分辨率下的帧率。此外,随着Cu-Cu连接间距减小的进展,最近的研究和开发提出了集成像素并行数字转换架构和AI信号处理器的CMOS图像传感器,并且它们将继续向更广泛的实际应用领域发展。

图21 CMOS图像传感器3D堆叠技术和架构的演进及未来趋势。为了更优化、更高效地集成光电二极管、像素电路、ADC、数字处理器和存储器等功能模块,需要能够进一步实现多层化、区块化的多层堆叠技术。

这些半导体技术的发展,有望进一步加速CMOS图像传感器的使用和新应用的开发,不断改善我们的生活。

补充国外网站关于sensor的一篇评论,是2020年的,https://semiengineering.com/scaling-cmos-image-sensors/,https://www.nikon.com/news/2021/0303_cmos_01.htm