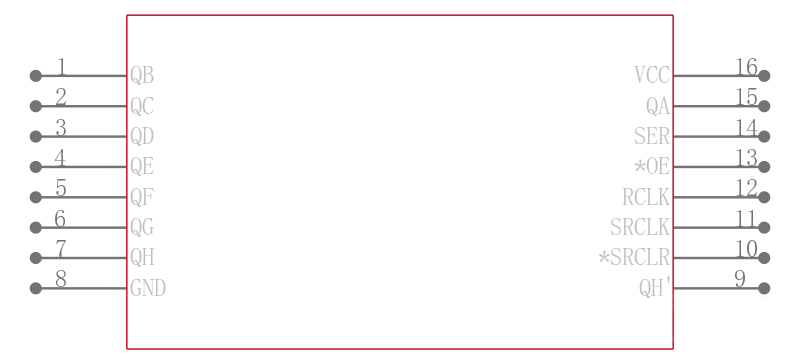

SN74LV595APWT

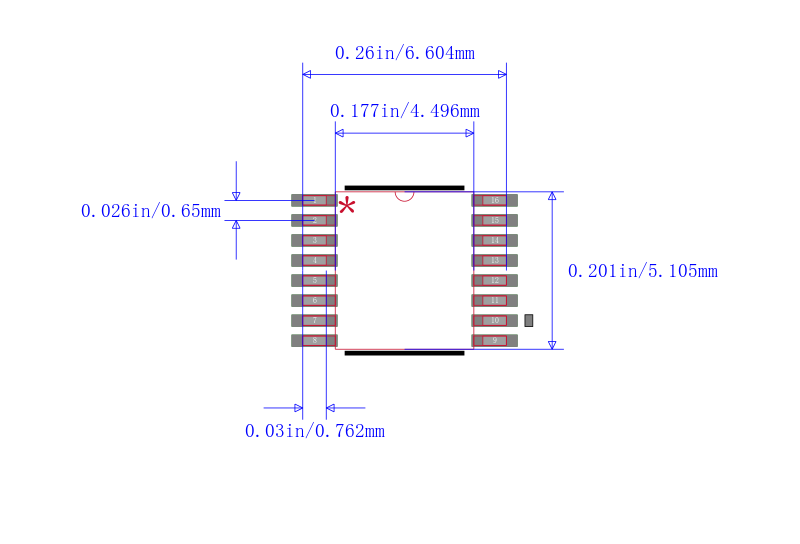

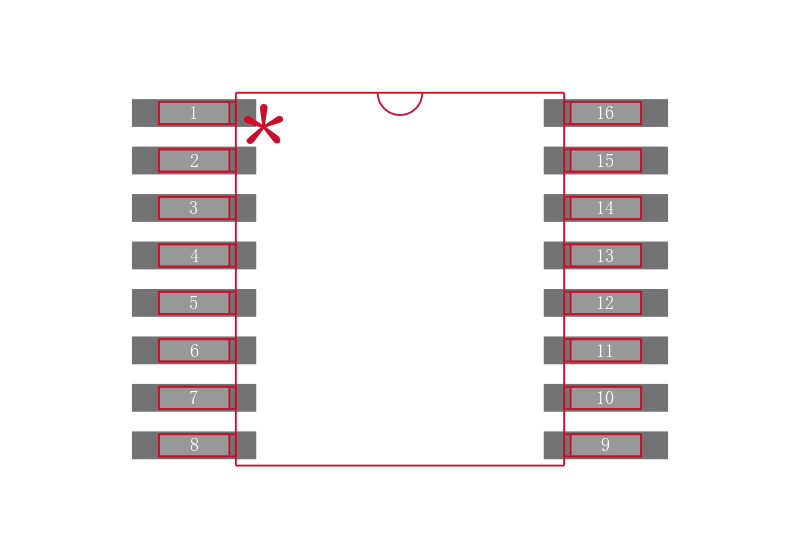

TEXAS INSTRUMENTS SN74LV595APWT 移位寄存器, LV系列, 串行至并行, 1元件, TSSOP, 16 引脚, 2 V, 5.5 V

The is a 8-bit serial-in parallel-out Shift Register feeds an 8-bit D-type storage register. The storage register has parallel 3-state outputs. Separate clocks are provided for the shift and storage registers. The shift register has a direct overriding clear SRCLR\\ input, serial SER input and serial outputs for cascading. When the OE\ input is high, the outputs are in the high-impedance state. Both the shift register clock SRCLK and storage register clock RCLK are positive-edge triggered. If both clocks are connected together, the shift register always is one clock pulse ahead of the storage register. This low-drive CMOS device can be used for a multitude of bus interface type applications where output ringing is a concern. The low drive and slow edge rates will minimize overshoot and undershoot on the outputs. The inputs are 5V tolerant allowing for down translation to VCC.

- .

- Support mixed-mode voltage operation on all ports

- .

- Ioff Supports live insertion, partial power-down mode and back-drive protection

- .

- Shift register has direct clear

- .

- Latch-up performance exceeds 250mA per JESD 17

- .

- Green product and no Sb/Br