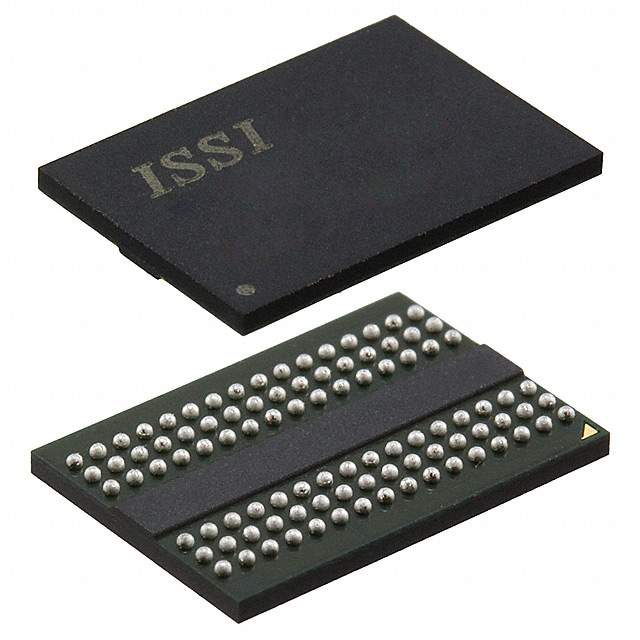

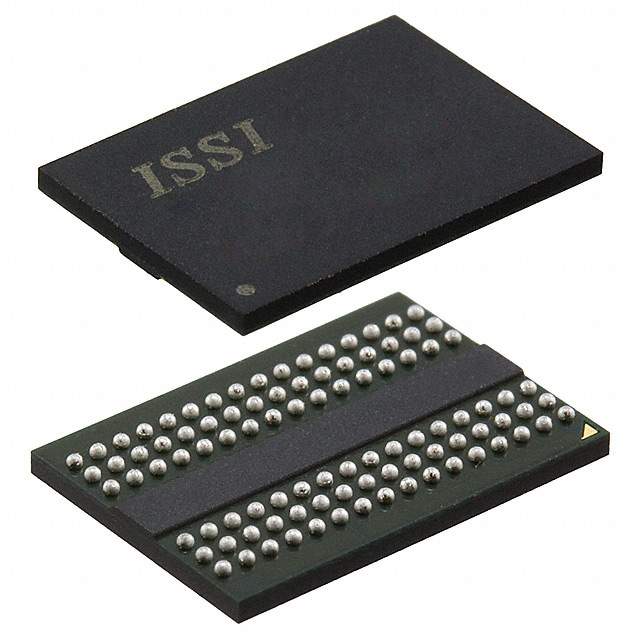

IS46LR16320B-6BLA1

动态随机存取存储器 512M 16Mx32 1.8v Mobile DDR S动态随机存取存储器

* JEDEC standard 1.8V power supply * Vdd = 1.8V, Vddq = 1.8V * Four internal banks for concurrent operation * MRS cycle with address key programs * CAS latency 2, 3 clock * Burst length 2, 4, 8, 16 * Burst type sequential and interleave * Fully differential clock inputs CK, /CK * All inputs except data and DM are sampled at the rising edge of the system clock * Data I/O transaction on both edges of data strobe * Bidirectional data strobe per byte of data DQS * DM for write masking only * Edge aligned data and data strobe output * Center aligned data and data strobe input * 64ms refresh period 8K cycle * Auto and self refresh * Concurrent Auto Precharge * Maximum clock frequency up to 166MHZ * Maximum data rate up to 333Mbps/pin * Power Saving support * PASR Partial Array Self Refresh * Auto TCSR Temperature Compensated Self Refresh * Deep Power Down Mode * Programmable Driver Strength Control by Full Strength or 1/2, 1/4, 1/8 of Full Strength * LVCMOS compatible inputs/outputs * 60-Ball FBGA package.Automotive Temperature Available.