TLK2201AJRZQE

1.0GB到1.6GB小尺寸以太网收发器 1.0Gb to 1.6Gb SMALL FORM-FACTOR ETHERNET TRANSCEIVER

The TLK2201AJR is a member of the transceiver family of multigigabit transceivers, optimized for use with small form-factor optical transceivers that require footprints smaller than 14 mm. The TLK2201AJR gigabit ethernet transceiver is fully compliant with IEEE 802.3 requirements for serializer/deserializer functions at 1.25 Gbps. The TLK2201AJR supports a wide range of serial data rates from 1.0 Gbps to 1.6 Gbps.

The primary application of this device is to provide building blocks for point-to-point baseband data transmission over controlled impedance media of 50 . The transmission media can be printed-circuit board traces, copper cables, or fiber-optical media. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

The TLK2201AJR performs the data serialization, deserialization, and clock extraction functions for a physical layer interface device. The transceiver operates at 1.25 Gbps typical, providing up to 1.0 Gbps of data bandwidth over a copper or optical media interface.

The TLK2201AJR supports both the defined 10-bit interface TBI and a reduced 5-bit interface with double data rate DDR clocking. In the TBI mode the serializer/deserializer serdes accepts 10-bit wide 8-bit/10-bit 8b/10b parallel encoded data bytes. The parallel data bytes are serialized and transmitted differentially at PECL compatible voltage levels. The serdes extracts clock information from the input serial stream and deserializes the data, outputting a parallel 10-bit data byte.

In the DDR mode the parallel interface accepts 5-bit wide 8-bit/10-bit encoded data aligned to both the rising and falling edge of the reference clock. The data is clocked most significant bit first i.e., bits 0-4 of the 8-bit/10-bit encoded data on the rising edge of the clock, and the least significant bits i.e., bits 5-9 of the 8-bit/10-bit encoded data are clocked on the falling edge of the clock.

The transceiver automatically locks onto incoming data without the need to prelock.

The TLK2201AJR provides a comprehensive series of built-in tests for self-test purposes including loopback and PRBS generation and verification. An IEEE 1149.1 JTAG port is also supported.

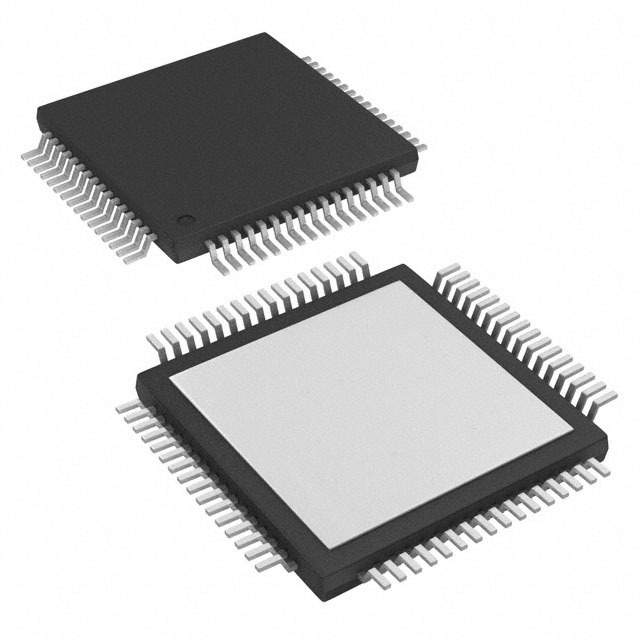

The TLK2201AJR is housed in a high-performance, thermally enhanced, 80-pin land grid array LGA MicroStarJr package. Use of the MicroStarJr™ package does not require any special considerations. All ac performance specifications in this data sheet are measured with the MicroStarJr™ soldered to the test board.

The TLK2201AJR is characterized for operation from 0°C to 70°C.

The TLK2201AJR uses a 2.5-V supply. The I/O section is 3.3-V compatible. With the 2.5-V supply the chipset is very power efficient dissipating less than 250 mW typical power when operating at 1.25 Gbps.

The TLK2201AJR is designed to be hot plug capable. A power-on reset holds RCB0 and RCB1 low. The parallel side output pins, TXP and TXN go to high-impedance during power up.