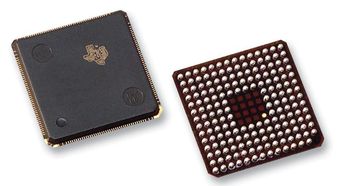

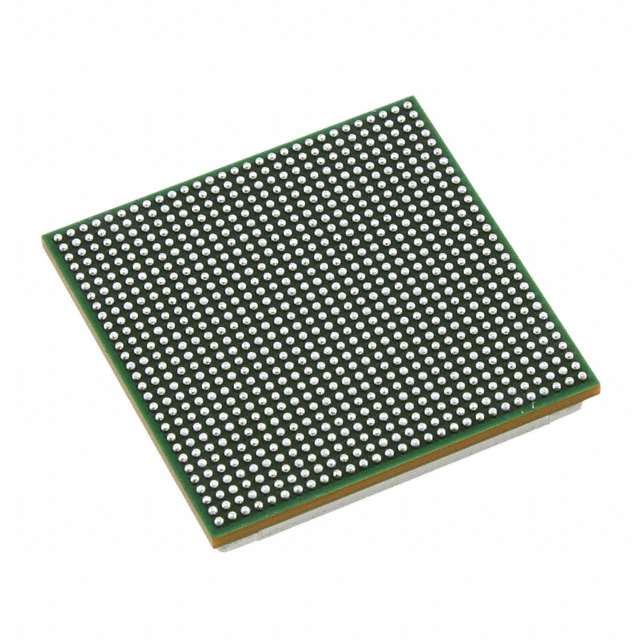

TMS320C203PZ80

数字信号处理器 DIGITAL SIGNAL PROCESSORS

* Based Upon the T320C2xLP Core CPU * 16-Bit Fixed-Point DSP Architecture * Six Internal Buses for Increased Parallelism and Performance * 32-Bit ALU/Accumulator * 16 × 16-Bit Single-Cycle Multiplier With a 32-Bit Product * Block Moves for Data, Program, I/O Space * Hardware Repeat Instruction * Instruction Cycle Time * "C203"LC203"C209 * 50 ns @ 5 V50 ns @ 3.3 V50 ns @ 5 V * 35 ns @ 5 V35 ns @ 5 V * 25 ns @ 5 V * Source Code Compatible With TMS320C25 * Upwardly Code-Compatible With TMS320C5x Devices * Four External Interrupts * Boot-Loader Option "C203 Only * TMS320C2xx Integrated Memory: * 544 × 16 Words of On-Chip Dual-Access Data RAM * 4K × 16 Words of On-Chip Single-Access Program/Data RAM "C209 only * 4K × 16 Words of On-Chip Program ROM "C209 Only * 224K × 16-Bit Total Addressable External Memory Space * 64K Program * 64K Data * 64K I/O * 32K Global * TMS320C2xx Peripherals: * PLL With Various Clock Options * -×1, ×2, ×4, 2 "C203 * -×2, 2 "C209 * On-Chip Oscillator * One Wait State Software-Programmable to Each Space "C209 Only * 0 - 7 Wait States Software-Programmable to Each Space "C203 Only * Six General-Purpose I/O Pins * On-Chip 20-Bit Timer * Full-Duplex Asynchronous Serial Port UART "C203 Only * One Synchronous Serial Port With Four-Level-Deep FIFOs "C203 Only * Supports Hardware Wait States * Designed for Low-Power Consumption * Fully Static CMOS Technology * Power-Down IDLE Mode * 1.1 mA/MIPS at 3.3 V * "C203 is Pin-Compatible With TMS320F206 Flash DSP * Up to 40-MIPS Performance at 5 V "C203 * 20-MIPS Performance at 3.3 V * HOLD Mode for Multiprocessor Applications * IEEE-1149.1-Compatible Scan-Based Emulation * 80- and 100-pin Small Thin Quad Flat Packages TQFPs, PN and PZ Suffixes