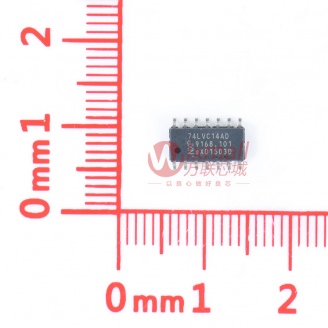

74LVC240AD

74LVC 系列,NXP低电压 CMOS 逻辑 工作电压:1.2 至 3.6 兼容性:输入 LVTTL/TTL、输出 LVCMOS ### 74LVC 系列

General description

The 74LVC240A is an octal inverting buffer/line driver with 3-state outputs. The 3-state outputs are controlled by the output enable inputs 1OEand 2OE. A HIGH on nOEcauses the outputs to assume a high-impedance OFF-state. Schmitt trigger action at all inputs makes the circuit highly tolerant of slower input rise and fall times.

Features and benefits

5 V tolerant inputs for interlacing with 5 V logic

Supply voltage range from 1.2 V to 3.6 V

CMOS low power consumption

Direct interface with TTL levels

High-impedance when VCC= 0 V

Complies with JEDEC standard:

JESD8-7A 1.65 V to 1.95 V

JESD8-5A 2.3 V to 2.7 V

JESD8-C/JESD36 2.7 V to 3.6 V

ESD protection:

HBM JESD22-A114F exceeds 2000 V

MM JESD22-A115B exceeds 200 V

CDM JESD22-C101E exceeds 1000 V

Specified from 40C to +85C and 40C to +125C