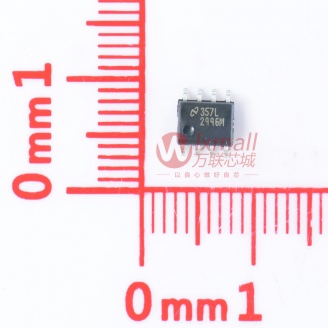

LP2996-N

具有关断引脚的 1.5A DDR 终端稳压器

The and LP2996A linear regulators are designed to meet the JEDEC SSTL-2 specifications for termination of DDR-SDRAM. The device also supports DDR2, while LP2996A supports DDR3 and DDR3L VTT bus termination with VDDQ minimum of 1.35 V. The device contains a high-speed operational amplifier to provide excellent response to load transients. The output stage prevents shoot through while delivering 1.5-A continuous current and transient peaks up to 3 A in the application as required for DDR-SDRAM termination. The LP2996-N and LP2996A also incorporate a VSENSE pin to provide superior load regulation and a VREF output as a reference for the chipset and DIMMs.

An additional feature found on the LP2996-N and LP2996A is an active-low shutdown SD pin that provides Suspend To RAM STR functionality. When SD is pulled low the VTT output will tri-state providing a high impedance output, but VREF remains active. A power savings advantage can be obtained in this mode through lower quiescent current.

recommends the LP2998 and LP2998-Q1 devices for automotive applications and DDR applications that require operating at temperatures below zero.

WEBENCH® design tools can be used by application designers to generate, optimize, and simlulate applications using the LP2998 and LP2998-Q1.

- .

- Minimum VDDQ:

- .

- 1.8 V LP2996-N

- .

- 1.35 V LP2996A

- .

- Source and Sink Current

- .

- Low Output Voltage Offset

- .

- No External Resistors Required for Setting Output Voltage

- .

- Linear Topology

- .

- Suspend to Ram STR Functionality

- .

- Stable With Ceramic Capacitors With Appropriate ESR

- .

- Low External Component Count

- .

- Thermal Shutdown