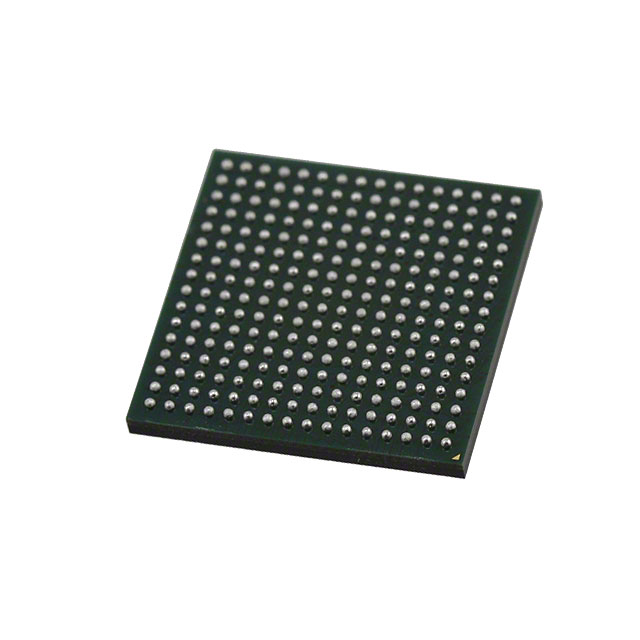

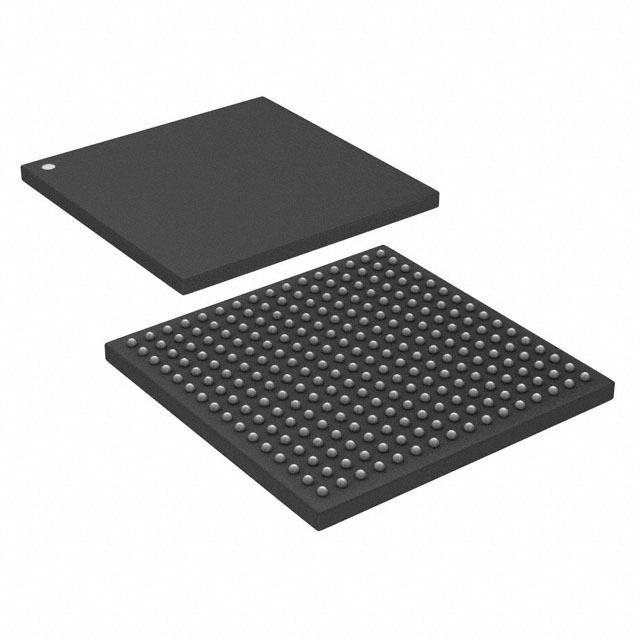

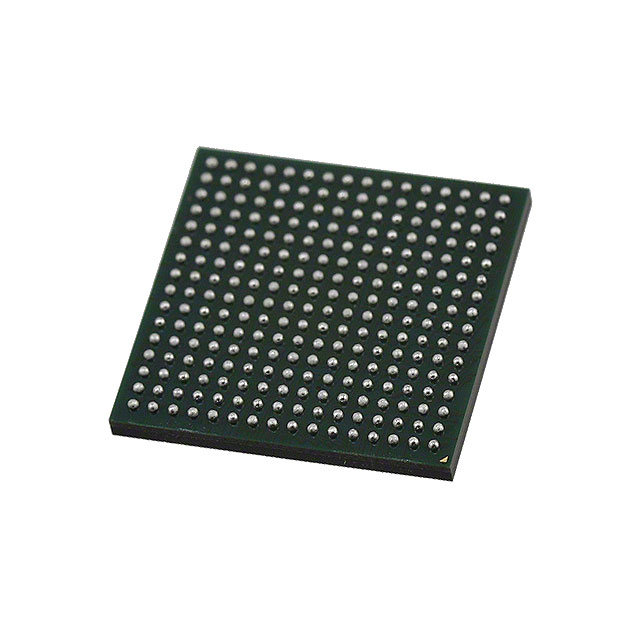

DS34S132GNA2+

Ic 32Port Tdm Over Packet 676bga

* 32 Independent TDM Ports with Serial Data, Clock, and Sync Data = 64Kbps to 2.048Mbps * One 100/1000Mbps MII/GMII Ethernet MAC * 256 Total PWs, 32 PW per TDM Port, with Any Combination of TDMoP and/or HDLC PWs * PSN Protocols: L2TPv3 or UDP Over IP IPv4 or IPv6, Metro Ethernet MEF-8, or MPLS MFA-8 * 0, 1, or 2 VLAN Tags IEEE 802.1Q * Synchronous or Asynchronous TDM Port Timing * One Clock Recovery Engine per TDM Port with One Assignable as a Global Reference * Supported Clock Recovery Techniques * Adaptive Clock Recovery * Differential Clock Recovery * Absolute and Differential Timestamps * Independent Receive and Transmit Interfaces * Two Clock Inputs for Direct Transmit Timing * For Structured T1/E1, Each TDM Port Includes * DS0 TSA Block for any Time Slot to Any PW * 32 HDLC/CES Engines 256 Total * With or Without CAS Signaling * For Unstructured, each TDM Port Includes * One HDLC/SAT Engine 32 Total * Any data rate from 64Kbps to 2.048Mbps * 32-Bit or 16-Bit CPU Processor Bus * CPU-Based OAM and Signaling * UDP-specific "Special" Ethernet Type * Inband VCCV ARP * MEF OAM * Broadcast DA * NDP/IPv6 * DDR SDRAM Interface * Low-Power 1.8V Core, 3.3V I/O, 2.5V SDRAM