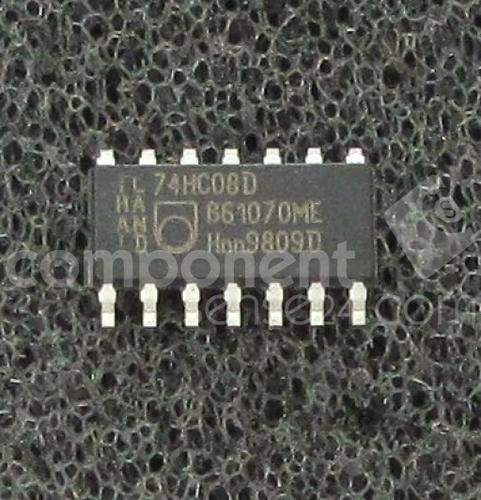

74HC4520D

NXP 74HC4520D 芯片, 逻辑电路 - 74HC, 计数器, SO16

The is a dual 4-bit internally synchronous Binary Counter with two clock inputs nCP0 and nCP1\\. It has buffered outputs from all 4-bit positions nQ0 to nQ3 and an asynchronous master reset input nMR. The counter advances on the low-to-high transition of nCP0 when nCP1\ is high. It also advances on the high-to-low transition of nCP1\ when nCP0 is low. Either nCP0 or nCP1 may be used as the clock input to the counter. The other clock input may be used as a clock enable input. A high on nMR, resets the counter nQ0 to nQ3 = low independent of nCP0 and nCP1\\. Inputs include clamp diodes. It enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

- .

- CMOS Input levels

- .

- Complies with JEDEC standard No. 7A