74HC73D

Dual JK flip-flop with reset; negative-edge trigger

General description

The 74HC73 is a high-speed Si-gate CMOS device and is pin compatible with low-power Schottky TTL LSTTL. The 74HC73 is specified in compliance with JEDEC standard no. 7A.

Features

Low-power dissipation

Complies with JEDEC standard no. 7A

ESD protection:

◆HBM EIA/JESD22-A114-B exceeds 2000 V

◆MM EIA/JESD22-A115-A exceeds 200 V.

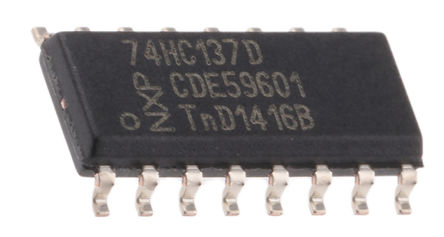

Multiple package options

Specified from−40°Cto+80°C and from−40°C to +125°C.