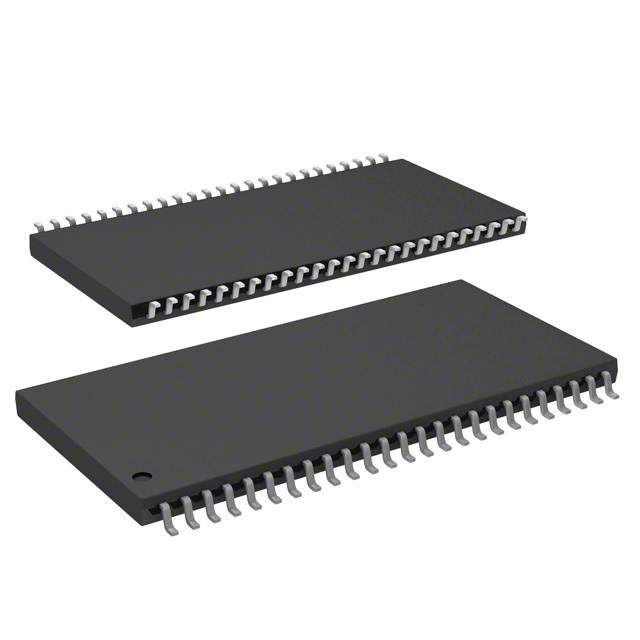

IS42S16400F-7TLI

INTEGRATED SILICON SOLUTION ISSI IS42S16400F-7TLI 存储芯片, SDRAM, IND, 4M X 16, 3V, 54TSOP2

The is a 64Mb Synchronous DRAM is organized as 1,048,576 bits x 16-bit x 4-bank for improved performance. The synchronous DRAMs achieve high-speed data transfer using pipeline architecture. All inputs and outputs signals refer to the rising edge of the clock input. The 64Mb SDRAM is a high speed CMOS, dynamic random-access memory designed to operate in 3.3V memory systems containing 67,108,864 bits. Internally configured as a quad-bank DRAM with a synchronous interface. Each 16,777,216-bit bank is organized as 4,096 rows by 256 columns by 16 bits. The 64Mb SDRAM includes an AUTO REFRESH MODE and a power-saving, power-down mode. All signals are registered on the positive edge of the clock signal, CLK. All inputs and outputs are LVTTL compatible.

- .

- 143MHz Clock frequency

- .

- 7ns Speed

- .

- Fully synchronous, all signals referenced to a positive clock edge

- .

- Internal bank for hiding row access/precharge

- .

- Single 3.3V power supply

- .

- LVTTL interface

- .

- Programmable burst length - 1, 2, 4, 8, full page

- .

- Sequential/Interleave programmable burst sequence

- .

- Self refresh modes

- .

- Auto refresh CBR

- .

- 4096 Refresh cycles every 64 ms Com, Ind, A1 grade or 16ms A2 grade

- .

- Random column address every clock cycle

- .

- Programmable CAS latency - 2, 3 clocks

- .

- Burst read/write and burst read/single write operations capability

- .

- Burst termination by burst stop and precharge command