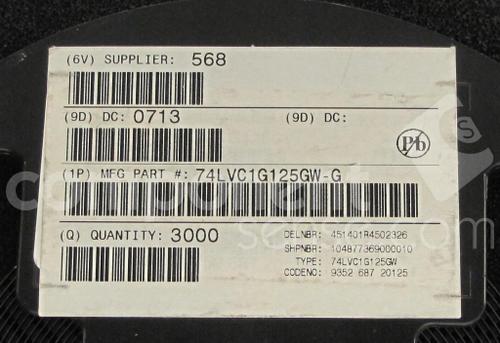

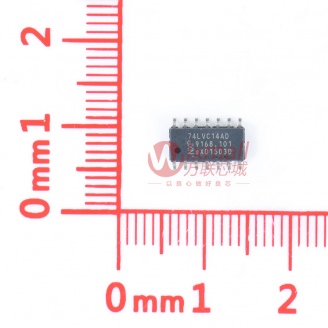

74LVT573PW,118

NXP 74LVT573PW,118 芯片, 锁存器, D型, 透明, 三态, TSSOP-20

The 74LVT573PW is an octal BiCMOS transparent D Latch designed for VCC operation at 3.3V. It is coupled to eight 3-state output buffers. The two sections of the device are controlled independently by LE and OE\ control gates. It has a broadside pinout configuration to facilitate PC board layout and allow easy interface with microprocessors. The data on the Dn inputs are transferred to the latch outputs when the LE input is high. The latch remains transparent to the data inputs while LE is high and stores the data that is present one setup time before the high-to-low enable transition. The 3-state output buffers are designed to drive heavily loaded 3-state buses, MOS memories or MOS microprocessors. The active-low OE\ controls all eight 3-state buffers independent of the latch operation. When OE\ is low, the latched or transparent data appears at the outputs.

- .

- Inputs and outputs arranged for easy interfacing to microprocessors

- .

- 3-state outputs for bus interfacing

- .

- Common output enable control

- .

- TTL input and output switching levels

- .

- Input and output interface capability to systems at 5V supply

- .

- Bus hold data inputs eliminate need for external pull-up resistors to hold unused inputs

- .

- Live insertion and extraction permitted

- .

- No bus current loading when output is tied to 5V bus

- .

- Power-up reset

- .

- Power-up 3-state

- .

- Latch-up protection