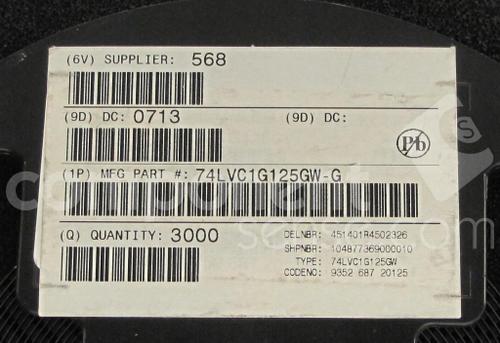

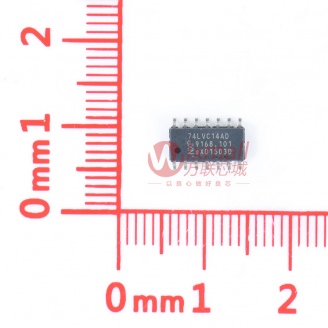

74LV14D,118

NXP 74LV14D,118 非门, LV系列, 施密特触发, 6输入, 25 mA, 1V至5.5V, SOIC-14

The 74LV14D is a low-voltage Si-gate CMOS device provides six Inverting buffers with Schmitt-trigger input. The device is pin and function compatible with 74HC14 and 74HCT14. The device is capable of transforming slowly-changing input signals into sharply defined, jitter-free output signals. The inputs switch at different points for positive and negative-going signals. The difference between the positive voltage VT+ and the negative voltage VT- is defined as the input hysteresis voltage VH.

- .

- Optimized for low voltage applications 1 to 3.6V

- .

- Accepts TTL input levels between VCC = 2.7V and VCC = 3.6V

- .

- <0.8V Output ground bounce

- .

- >2V High-level output voltage VOH undershoot

- .

- ESD protection - HBM JESD22-A114E exceeds 2000V, MM JESD22-A115-A exceeds 200V