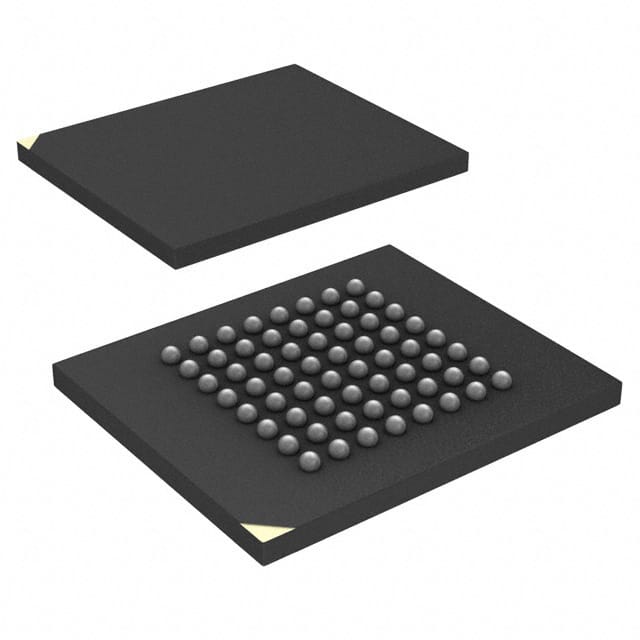

PC28F00AG18AE

Flash, 64MX16, 96ns, PBGA64, 8 X 10MM, 1.2MM HEIGHT, ROHS COMPLIANT, TBGA-64

General Description

"s 65nm device is the latest generation of StrataFlash® wireless memory featuring flexible, multiple-partition, dual-operation architecture. The device provides high performance, asynchronous read mode and synchronous-burst read mode using 1.8V low-voltage, multilevel cell MLC technology.

Features

• High-Performance Read, Program and Erase

– 96 ns initial read access

– 108 MHz with zero wait-state synchronous burst reads: 7 ns clock-to-data output

– 133 MHz with zero wait-state synchronous burst reads: 5.5 ns clock-to-data output

– 8-, 16-, and continuous-word synchronous-burst Reads

– Programmable WAIT configuration

– Customer-configurable output driver impedance

– Buffered Programming: 2.0 μs/Word typ, 512-Mbit 65 nm

– Block Erase: 0.9 s per block typ

– 20 μs typ program/erase suspend

• Architecture

– 16-bit wide data bus

– Multi-Level Cell Technology

– Symmetrically-Blocked Array Architecture

– 256-Kbyte Erase Blocks

– 1-Gbit device: Eight 128-Mbit partitions

– 512-Mbit device: Eight 64-Mbit partitions

– 256-Mbit device: Eight 32-Mbit partitions

– 128-Mbit device: Eight 16-Mbit partitions

– Read-While-Program and Read-While-Erase

– Status Register for partition/device status

– Blank Check feature

• Quality and Reliability

– Expanded temperature: –30 °C to +85 °C

– Minimum 100,000 erase cycles per block

– 65nm Process Technology

• Power

– Core voltage: 1.7 V - 2.0 V

– I/O voltage: 1.7 V - 2.0 V

– Standby current: 60 μA typ for 512-Mbit, 65 nm

– Deep Power-Down mode: 2 μA typ

– Automatic Power Savings mode

– 16-word synchronous-burst read current: 23 mA typ @ 108 MHz; 24 mA typ @ 133 MHz

• Software

– Micron® Flash data integrator FDI optimized

– Basic command set BCS and extended command set ECS compatible

– Common Flash interface CFI capable

• Security

– One-time programmable OTP space

64 unique factory device identifier bits

2112 user-programmable OTP bits

– Absolute write protection: VPP = GND

– Power-transition erase/program lockout

– Individual zero latency block locking

– Individual block lock-down

• Density and packaging

– 128Mb, 256Mb, 512Mbit, and 1-Gbit

– Address-data multiplexed and non-multiplexed interfaces

– 64-Ball Easy BGA