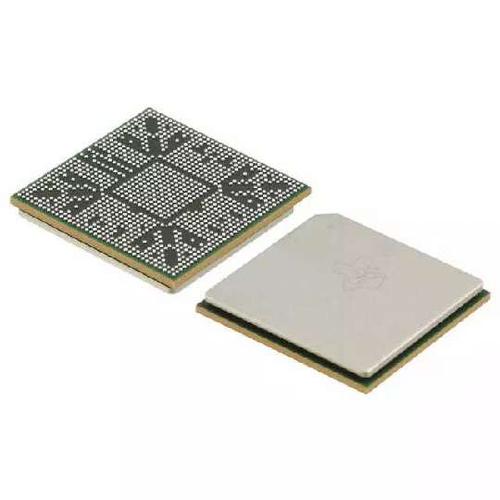

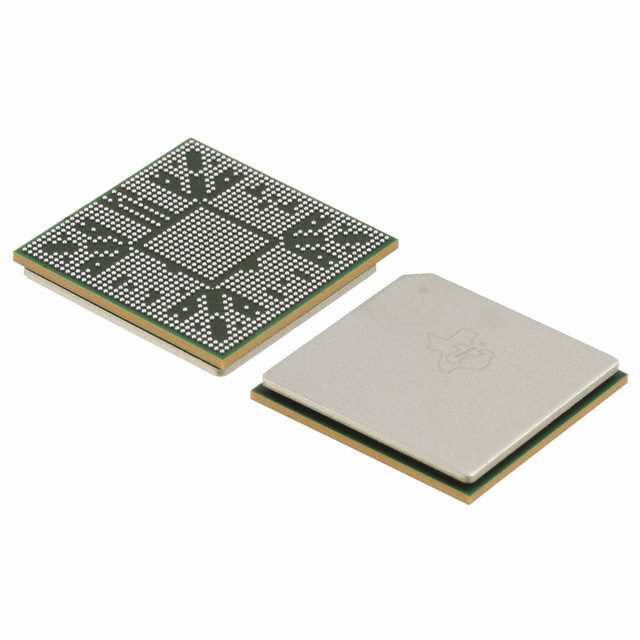

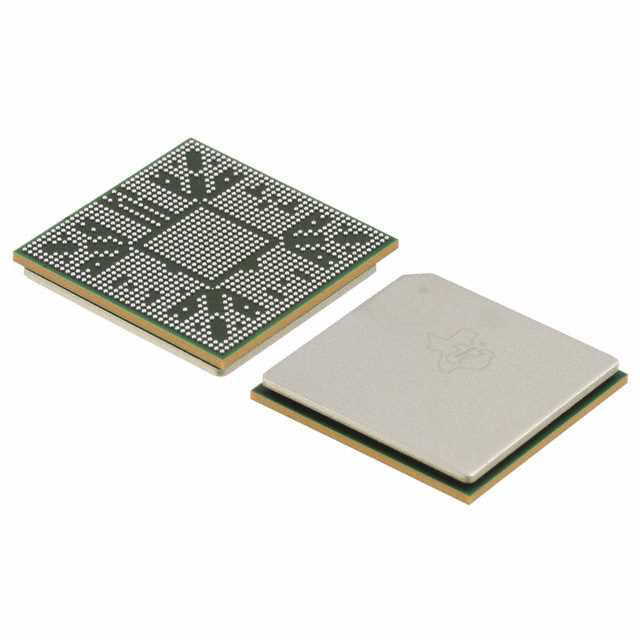

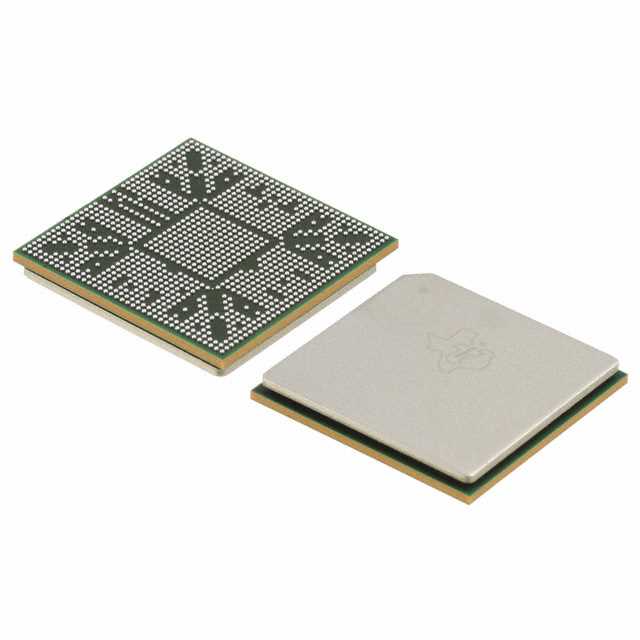

AM3871CCYE100

Sitara 处理器:Arm Cortex-A8、以太网 684-FCBGA 0 to 90

* High-PerformanceSitara ARM®Processors * ARM Cortex-A8Core * ARMv7 Architecture * In-Order, Dual-Issue, Superscalar Processor Core * Neon™ Multimedia Architecture * Supports Integer and Floating Point * Jazelle® RCT Execution Environment * ARM Cortex-A8 Memory Architecture * 32KB of Instruction and Data Caches * 512KB of L2 Cache * 64KB of RAM, 48KB of Boot ROM * 128KBof On-Chip Memory Controller OCMC RAM * Imaging Subsystem ISS * Camera Sensor Connection * Parallel Connection for Raw up to 16-Bit and BT.656 or BT.1120 8- and 16-Bit * Image Sensor Interface ISIF for Handling Image and Video Data From the Camera Sensor * Resizer * Resizing Image and Video From 1/16x to 8x * Generating Two Different Resizing Outputs Concurrently * Media Controller * Controls the HDVPSS and ISS * SGX530 3D Graphics Engine * Delivers up to 25 MPoly/sec * Universal Scalable Shader Engine * Direct3D Mobile, OpenGLES 1.1 and 2.0, OpenVG 1.0, OpenMax API Support * Advanced Geometry DMA Driven Operation * Programmable HQ Image Anti-Aliasing * Endianness * ARM Instructions/Data – Little Endian * HD VideoProcessing Subsystem HDVPSS * Two 165-MHz, 2-channel HD Video Capture Modules * One 16-/24-Bit Input or Dual 8-Bit SD Input Channels * One 8-/16-/24-Bit Input and One 8-Bit Only Input Channels * Two 165-MHz HD Video Display Outputs * One 16-, 24-, or 30-Bit Output and One 16- or 24-Bit Output * Composite or S-Video Analog Output * Macrovision® Support Available * Digital HDMI 1.3 Transmitter With Integrated PHY * Advanced Video Processing Features Such as Scan, Format, Rate Conversion * Three Graphics Layers and Compositors * Dual 32-BitDDR2/DDR3 SDRAM Interfaces * Supports up to DDR2-800 and DDR3-1066 * Up to Eight x 8 Devices Total 2GB of Total Address Space * Dynamic Memory Manager DMM * Programmable Multi-Zone Memory Mapping and Interleaving * Enables Efficient 2D Block Accesses * Supports Tiled Objects in 0°, 90°, 180°, or 270° Orientation and Mirroring * Optimizes Interlaced Accesses * General-Purpose Memory ControllerGPMC * 8- or 16-Bit Multiplexed Address and Data Bus * 512MB of Address Space Divided Among up to 8 Chip Selects * Glueless Interface to NOR Flash, NAND Flash BCH/Hamming Error Code Detection, SRAM and Pseudo-SRAM * Error Locator Module ELM Outside of GPMC to Provide Up to 16-Bit or 512-Byte Hardware ECC for NAND * Flexible Asynchronous Protocol Control for Interface to FPGA, CPLD, ASICs, and so Forth * Enhanced Direct Memory Access EDMAController * Four Transfer Controllers * 64 Independent DMA Channels and 8 Independent QDMA Channels * Dual Port Ethernet10/100/1000 Mbps With Optional Switch * IEEE 802.3 Compliant 3.3-V I/O Only * MII/RMII/GMII/RGMII Media Independent Interfaces * Management Data I/O MDIO Module * Reset Isolation * IEEE 1588 Time-Stamping and Industrial Ethernet Protocols * Dual USB 2.0 Ports WithIntegrated PHYs * USB2.0 High- and Full-Speed Clients * USB2.0 High-, Full-, and Low-Speed Hosts, or OTG * Supports End Points 0–15 * OnePCI Express 2.0 Port With Integrated PHY * Single Port With One Lane at 5.0 GT/s * Configurable as Root Complex or Endpoint