CK-V7-VC7203-G-J

表征套件, Virtex-7 FPGA, IBERT, Vivado, 仅限日本

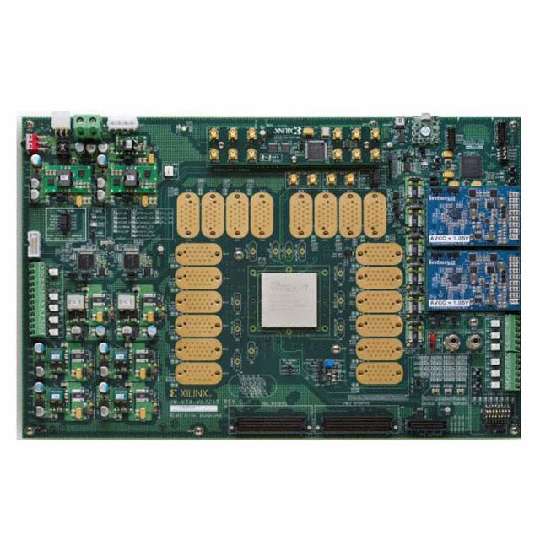

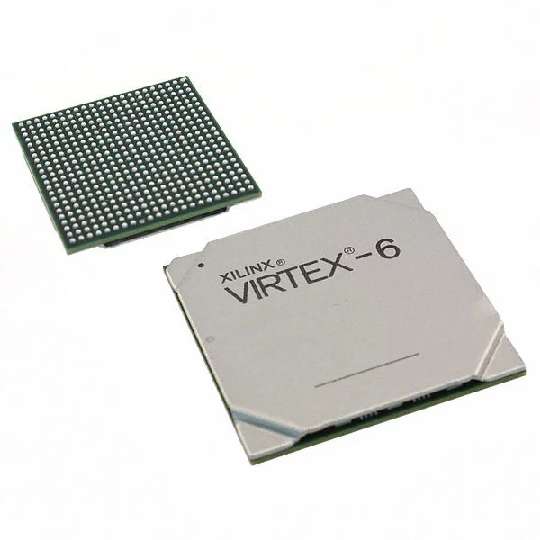

The from is a Virtex-7 FPGA VC7203 characterization kit Japan specific. The Virtex®-7 FPGA VC7203 characterization kit provides the hardware environment for characterizing and evaluating 28 GTX 12.5Gbps transceivers of the on-board Virtex-7 V485T FPGA. The VC7203 allows evaluation of the Integrated Bit Error Ratio Test IBERT demonstration using either the Vivado™ or ISE® design suites. Each GTX quad and its associated reference clock are routed from the FPGA to a connector pad which is designed to interface with a Samtec BullsEye connector. A cable enabled with a BullsEye connector and 10 standard SMAs allows users to connect to a broad range of evaluation platforms, from backplanes and optical evaluation boards to high speed test equipment. Each BullsEye connector handles a full GTX quad, four transmit/receive pairs as well as the two independent reference clocks, enabling the highest level of flexibility in testing custom applications.

- .

- Hardware, design tools, IP and pre-verified reference designs

- .

- Integrated Bit Error Ratio Test IBERT reference design

- .

- BullsEye connector supporting a full GTX quad with four transmit/receive pairs

- .

- Nine Samtec BullsEye connector pads for the GTX transceivers and reference clocks

- .

- Two pairs of differential MRCC inputs with SMA connectors

- .

- System ACE™ SD controller memory, Digilent USB JTAG programming port configuration

- .

- Expand I/O with 3 FPGA Mezzanine Card FMC interface, 485760 logic cells, 2800 DSP slices

- .

- Power status LEDs and general purpose DIP switches, LEDs, push buttons and test I/O display

- .

- SuperClock-2 module supporting multiple frequencies, 37080Kb memory

- .

- Fixed, 200MHz 2.5V LVDS oscillator wired to multi region clock capable MRCC inputs clocking