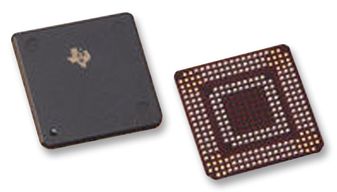

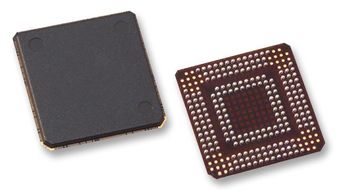

PCI2060IGHK

PCI接口IC Async 32-Bit 66MHz PCI-to-PCI Bridge

The Texas Instruments PCI2060 is a 32-bit, asynchronous, PCI-to-PCI bridge that is fully compliant with the _PCI Local Bus Specification_, Revision 2.3 and the _PCI-to-PCI Bridge Specification_, Revision 1.1. The PCI2060 bridge makes it possible for the primary and secondary bus clocks to be completely asynchronous and supports the PCI clock frequency up to 66 MHz.

The PCI2060 bridge is architecture-configurable for the _PCI Bus Power Interface Specification_. It can be configured to support either revision 1.0 or revision 1.1. Power conservation is made possible by using 1.8-V core logic with a universal PCI interface compatible with 3.3-V and 5-V PCI signaling environments.

The PCI2060 bridge allows the primary and secondary buses to operate concurrently. It provides independent read and write buffers for each direction and utilizes pipeline architecture for burst data transfer.

The PCI2060 bridge makes it possible to overcome the electrical loading limit of ten devices per PCI bus and one PCI device per expansion slot by creating hierarchical buses. Each PCI2060 bridge that is added to the system creates a new PCI bus. The PCI2060 bridge provides a two-tier internal arbitration for up to nine secondary bus masters and may be implemented with an external arbiter.

The PCI2060 bridge provides CompactPCI hot-swap support that is compliant with the _PICMG CompactPCI Hot-Swap Specification_, Revision 1.0.