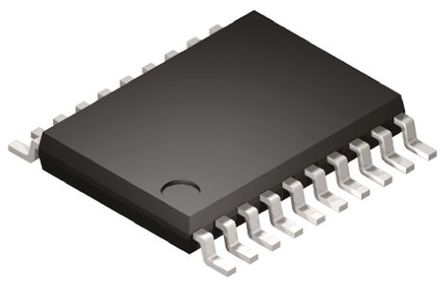

74AC11175DWR

Flip Flop D-Type Bus Interface Pos-Edge 1Element 20Pin SOIC T/R

description

These positive-edge-triggered flipflops implement D-type flip-flop logic with a direct clear input. Information at the D inputs that meets the setup time requirements is transferred to the outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the high or low level, the D input signal has no effect at the output.

• Applications Include: Buffer/Storage Registers, Shift Registers, Pattern Generators

• Flow-Through Architecture Optimizes PCB Layout

• Center-Pin VCC and GND Configurations Minimize High-Speed Switching Noise

• EPIC™Enhanced-Performance Implanted CMOS 1-μm Process

• 500-mA Typical Latch-Up Immunity at 125°C

• Package Options Include Plastic

Small-Outline Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs