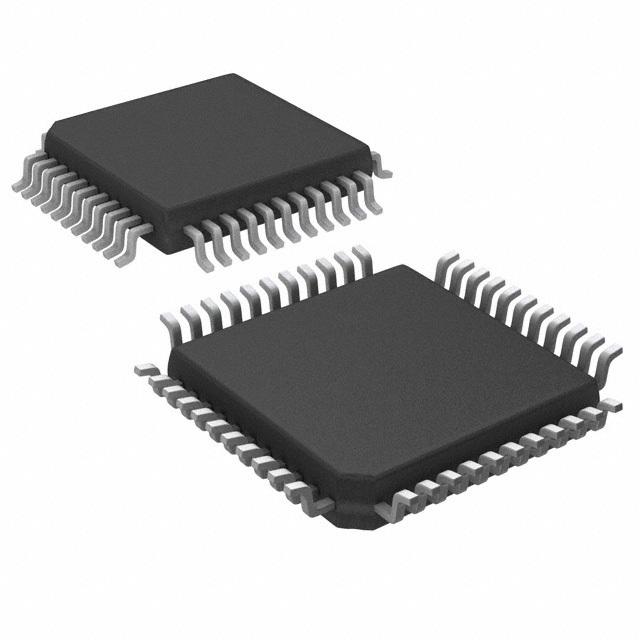

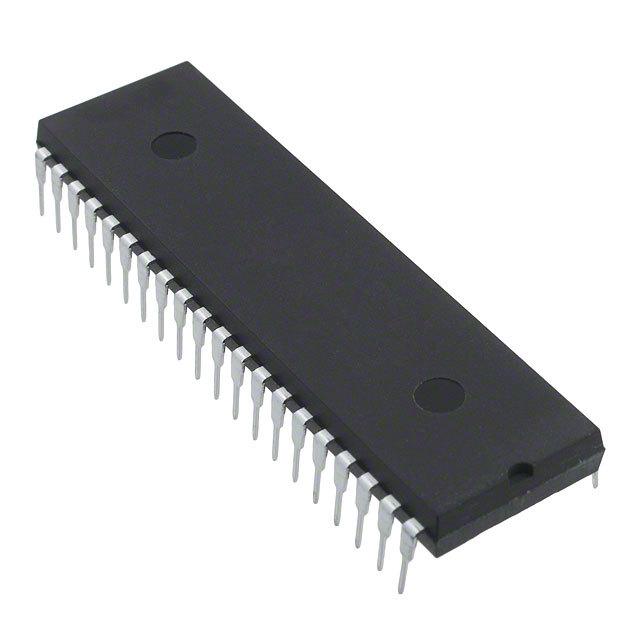

P80C31SBBB,557

MCU 8Bit P80 80C51 CISC ROM 3.3V/5V 44Pin PQFP

The is a 8-bit Microcontroller based on high-performance static 80C51 design fabricated with high-density CMOS. The device contain a 128 x 8 RAM, 32 I/O lines, three 16-bit counter/timers, a six-source, four-priority level nested interrupt structure, a serial I/O port for either multi-processor communications, I/O expansion or full duplex UART and on-chip oscillator and clock circuits. The device is a low power static design which offers a wide range of operating frequencies down to zero. Two software selectable modes of power reduction idle mode and power-down mode are available. The idle mode freezes the CPU while allowing the RAM, timers, serial port and interrupt system to continue functioning. The power-down mode saves the RAM contents but freezes the oscillator, causing all other chip functions to be inoperative. Since the design is static, the clock can be stopped without loss of user data and then the execution resumed from the point the clock was stopped.

- .

- 8051 Central processing unit

- .

- Boolean processor

- .

- Full static operation

- .

- Memory addressing capability - 64k ROM and 64k RAM

- .

- Clock can be stopped and resumed

- .

- Idle mode

- .

- Power-down mode

- .

- CMOS and TTL compatible

- .

- 2 Speed ranges at VCC = 5V - 0 to 16MHz, 0 to 33MHz

- .

- Dual data pointers

- .

- 4 Level priority interrupt

- .

- 6 Interrupt sources

- .

- Four 8-bit I/O ports

- .

- Full duplex enhanced UART

- .

- Programmable clock out

- .

- Asynchronous port reset

- .

- Low EMI inhibit ALE

- .

- Wake-up from Power Down by an external interrupt