TMS320C6711BGFN100

浮点数字信号处理器 FLOATING-POINT DIGITAL SIGNAL PROCESSORS

description

The TMS320C67x DSPs including the TMS320C6711, TMS320C6711B, TMS320C6711C, TMS320C6711D devices† compose the floating-point DSP family in the TMS320C6000 DSP platform. The C6711, C6711B, C6711C, and C6711D devices are based on the high-performance, advanced very-long-instruction-word VLIW architecture developed by Texas Instruments , making these DSPs an excellent choice for multichannel and multifunction applications.

• Excellent-Price/Performance Floating-Point

Digital Signal Processors DSPs: TMS320C67x™ C6711, C6711B and C6711C

− Eight 32-Bit Instructions/Cycle

− 100-, 150-, 167-, 200-MHz Clock Rates

− 10-, 6.7-, 6-, 5-ns Instruction Cycle Time

− 600, 900, 1000, 1200 MFLOPS

• Advanced Very Long Instruction Word VLIW C67x™ DSP Core

− Eight Highly Independent Functional Units:

− Four ALUs Floating- and Fixed-Point

− Two ALUs Fixed-Point

− Two Multipliers Floating- and Fixed-Point

− Load-Store Architecture With 32 32-Bit General-Purpose Registers

− Instruction Packing Reduces Code Size

− All Instructions Conditional

• Instruction Set Features

− Hardware Support for IEEE Single-Precision and Double-Precision Instructions

− Byte-Addressable 8-, 16-, 32-Bit Data

− 8-Bit Overflow Protection

− Saturation

− Bit-Field Extract, Set, Clear

− Bit-Counting

− Normalization

• L1/L2 Memory Architecture

− 32K-Bit 4K-Byte L1P Program Cache Direct Mapped

− 32K-Bit 4K-Byte L1D Data Cache 2-Way Set-Associative

− 512K-Bit 64K-Byte L2 Unified Mapped RAM/Cache Flexible Data/Program Allocation

• Device Configuration

− Boot Mode: HPI, 8-, 16-, 32-Bit ROM Boot

− Endianness: Little Endian, Big Endian

• Enhanced Direct-Memory-Access EDMA Controller 16 Independent Channels

• 32-Bit External Memory Interface EMIF

− Glueless Interface to Asynchronous Memories: SRAM and EPROM

− Glueless Interface to Synchronous Memories: SDRAM and SBSRAM

− 256M-Byte Total Addressable External Memory Space

• 16-Bit Host-Port Interface HPI

• Two Multichannel Buffered Serial Ports McBSPs

− Direct Interface to T1/E1, MVIP, SCSA Framers

− ST-Bus-Switching Compatible

− Up to 256 Channels Each

− AC97-Compatible

− Serial-Peripheral-Interface SPI Compatible Motorola

• Two 32-Bit General-Purpose Timers

• Flexible Phase-Locked-Loop PLL Clock Generator [C6711/11B]

• Flexible Software Configurable PLL-Based Clock Generator Module [C6711C]

• A Dedicated General-Purpose Input/Output GPIO Module With 5 Pins [C6711C]

• IEEE-1149.1 JTAG†

Boundary-Scan-Compatible

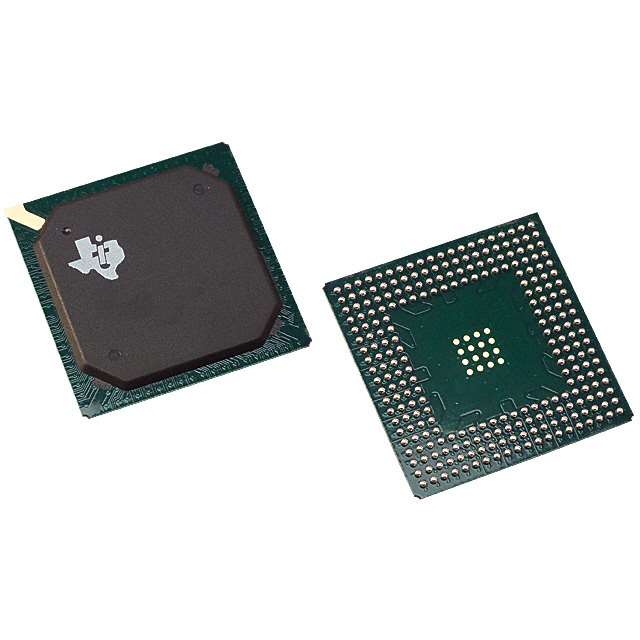

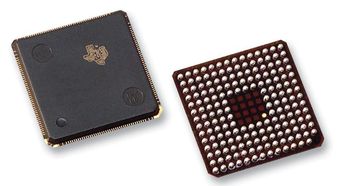

• 256-Pin Ball Grid Array BGA Package GFN Suffix [C6711/C6711B Only]

• 272-Pin Ball Grid Array BGA Package GDP Suffix [C6711C Only]

• CMOS Technology

− 0.13-µm/6-Level Copper Metal Process C6711C

− 0.18-µm/5-Level Copper Metal Process C6711/11B

• 3.3-V I/O, 1.20-V Internal C6711C‡

• 3.3-V I/O, 1.8-V Internal C6711B/C6711−100

• 3.3-V I/O, 1.9-V Internal C6711-150