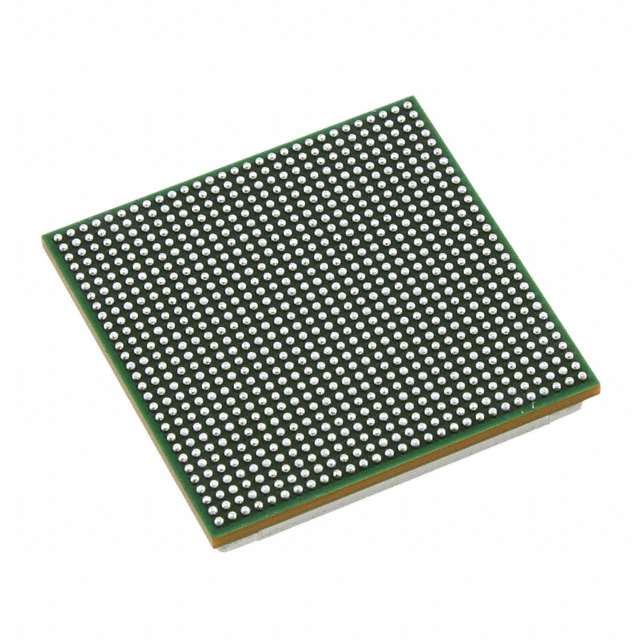

TMS320DM640AZDKA4

视频/影像定点数字信号处理器 Video/Imaging Fixed-Point Digital Signal Processors

The TMS320C64x™ DSPs including the TMS320DM641 and TMS320DM640 devices are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The TMS320DM641 DM641 and TMS320DM640 DM640 devices are based on the second-generation high-performance, advanced Veloci™ very-long-instruction-word VLIW architecture VelociTI.2™ developed by Texas Instruments TI, making these DSPs an excellent choice for digital media applications. The C64x™ is a code-compatible member of the C6000™ DSP platform.

With performance of up to 4800 million instructions per second MIPS at a clock rate of 600 MHz, the DM641 device offers cost-effective solutions to high-performance DSP programming challenges.

With performance of up to 3200 million instructions per second MIPS at a clock rate of 400 MHz, the DM640 device offers cost-effective solutions to high-performance DSP programming challenges.

The DM641/DM640 DSP possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x™ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units-two multipliers for a 32-bit result and six arithmetic logic units ALUs-with VelociTI.2™ extensions. The VelociTI.2™ extensions in the eight functional units include new instructions to accelerate the performance in video and imaging applications and extend the parallelism of the VelociTI™ architecture. The DM641 can produce four 16-bit multiply-accumulates MACs per cycle for a total of 2400 million MACs per second MMACS, or eight 8-bit MACs per cycle for a total of 4800 MMACS. The DM640 can produce four 16-bit multiply-accumulates MACs per cycle for a total of 1600 million MACs per second MMACS, or eight 8-bit MACs per cycle for a total of 3200 MMACS. The DM641/DM640 DSP also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000™ DSP platform devices.

The DM641/DM640 uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The Level 1 program cache L1P is a 128-Kbit direct mapped cache and the Level 1 data cache L1D is a 128-Kbit 2-way set-associative cache. The Level 2 memory/cache L2 consists of an 1-Mbit memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two. The peripheral set includes: two configurable video ports DM641; one configurable video port DM640; a 10/100 Mb/s Ethernet MAC EMAC; a management data input/output MDIO module; a VCXO interpolated control port VIC; one 4-bit multichannel buffered audio serial port McASP0; an inter-integrated circuit I2C Bus module; two multichannel buffered serial ports McBSPs; three 32-bit general-purpose timers; a 16-bit host-port interface HPI16; a 8-pin general-purpose input/output port GP0 with programmable interrupt/event generation modes; and a 32-bit glueless external memory interface EMIFA, which is capable of interfacing to synchronous and asynchronous memories and peripherals.

The DM641 device has two single-channel 8-bit configurable video port peripherals VP0 and VP1. The DM640 device has one single-channel 8-bit configurable video port peripheral VP0. These video port peripherals provide a glueless interface to common video decoder and encoder devices. The DM641/DM640 video port peripherals support multiple resolutions and video standards e. g., CCIR601 and ITU-.

These video port peripherals are configurable and can support either video capture and/or video display modes.

For more details on the Video Port peripherals, see the _TMS320C64x DSP Video Port/VCXO Interpolated Control VIC Port Reference Guide_ literature number SPRU629.

The McASP0 port supports one transmit and one receive clock zone, with four serial data pins which can be individually allocated to any of the two zones. The serial port supports time-division multiplexing on each pin from 2 to 32 time slots. The DM641/DM640 has sufficient bandwidth to support all 4 serial data pins transmitting a 192-kHz stereo signal. Serial data in each zone may be transmitted and received on multiple serial data pins simultaneously and formatted in a multitude of variations on the Philips Inter-IC Sound I2S format.

In addition, the McASP0 transmitter may be programmed to output multiple S/PDIF, IEC60958, AES-3, CP-430 encoded data channels simultaneously, with a single RAM containing the full implementation of user data and channel status fields.

McASP0 also provides extensive error-checking and recovery features, such as the bad clock detection circuit for each high-frequency master clock which verifies that the master clock is within a programmed frequency range.

The VCXO interpolated control VIC port provides digital-to-analog conversion with resolution from 9-bits to up to 16-bits. The output of the VIC is a single bit interpolated D/A output. For more details on the VIC port, see the _TMS320C64x DSP Video Port/VCXO Interpolated Control VIC Port Reference Guide_ literature number SPRU629.

The ethernet media access controller EMAC provides an efficient interface between the DM641/DM640 DSP core processor and the network. The DM641/DM640 EMAC supports both 10Base-T and 100Base-TX, or 10 Mbits/second Mbps and 100 Mbps in either half- or full-duplex, with hardware flow control and quality of service QOS support. The DM641/DM640 EMAC makes use of a custom interface to the DSP core that allows efficient data transmission and reception. For more details on the EMAC, see the _TMS320C6000 DSP Ethernet Media Access Controller EMAC / Management Data Input/Output MDIO Module Reference Guide_ literature number SPRU628.

The management data input/output MDIO module continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the system. Once a PHY candidate has been selected by the DSP, the MDIO module transparently monitors its link state by reading the PHY status register. Link change events are stored in the MDIO module and can optionally interrupt the DSP, allowing the DSP to poll the link status of the device without continuously performing costly MDIO accesses. For more details on the MDIO, see the _TMS320C6000 DSP Ethernet Media Access Controller EMAC / Management Data Input/Output MDIO Module Reference Guide_ literature number SPRU628.

The I2C0 port on the TMS320DM641/DM640 allows the DSP to easily control peripheral devices and communicate with a host processor. In addition, the standard multichannel buffered serial port McBSP may be used to communicate with serial peripheral interface SPI mode peripheral devices.

The DM641/DM640 has a complete set of development tools which includes: a new C compiler, an assembly optimizer to simplify programming and scheduling, and a Windows™ debugger interface for visibility into source code View datasheet View product folder