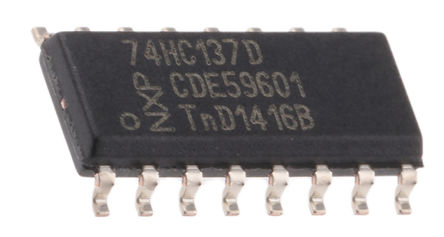

74HC112PW,118

NXP 74HC112PW,118 触发器, 互补输出, 负沿, JK, 66 MHz, TSSOP, 16 引脚

The 74HC112PW is a negative-edge trigger dual JK Flip-flop with set and reset. This high-speed Si-gate CMOS device is pin compatible with low power Schottky TTL LSTTL. It is specified in compliance with JEDEC standard no. 7A. This dual negative-edge triggered JK-type flip-flops featuring individual nJ, nK, clock nCP\\, set nSD\\ and reset nRD\\ inputs. The set and reset inputs, when low, set or reset the outputs as shown in the function table regardless of the levels at the other inputs. A HIGH level at the clock nCP input enables the nJ and nK inputs and data will be accepted. The nJ and nK inputs control the state changes of the flip-flops as shown in the function table. The nJ and nK inputs must be stable one set-up time prior to the high-to-low clock transition for predictable operation. Output state changes are initiated by the high-to-low transition of nCP. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

- .

- Asynchronous set and reset

- .

- Standard output capability

- .

- ICC Category