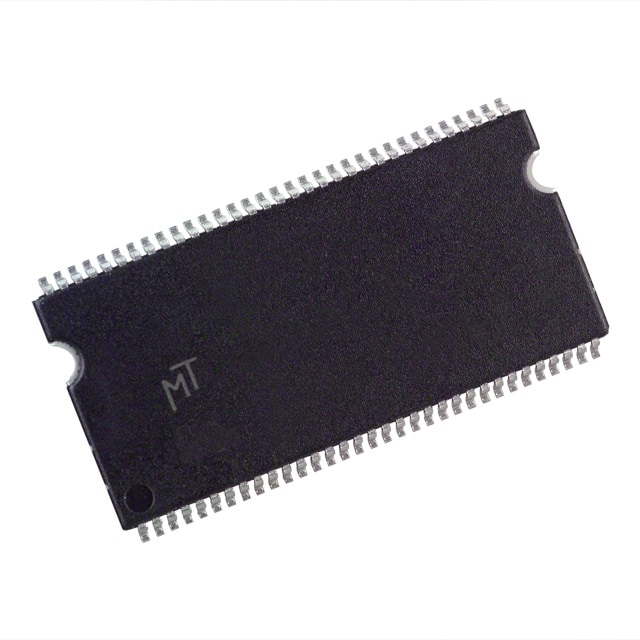

MT46V16M16CY-5BIT:M

DDR DRAM, 16MX16, 0.7ns, CMOS, PBGA60, 8 X 12.5MM, LEAD FREE, PLASTIC, FBGA-60

* VDD = 2.5V ±0.2V; VDDQ = 2.5V ±0.2V * VDD = 2.6V ±0.1V; VDDQ = 2.6V ±0.1V DDR400 * Bidirectional data strobe DQS transmitted/ received with data, that is, source-synchronous data capture x16 has two o one per byte * Internal, pipelined double data rate DDR architecture; two data accesses per clock cycle * Differential clock inputs CK and CK# * Commands entered on each positive CK edge * DQS edge-aligned with data for READs; center aligned with data for WRITEs * DLL to align DQ and DQS transitions with CK * Four internal banks for concurrent operation * Data mask DM for masking write data x16 has two o one per byte * Programmable burst lengths BL: 2, 4, or 8 * Auto refresh * 64ms, 8192-cycle * Longer-lead TSOP for improved reliability OCPL * 2.5V I/O SSTL_2-compatible * Concurrent auto precharge option supported * tRAS lockout supported tRAP = tRCD