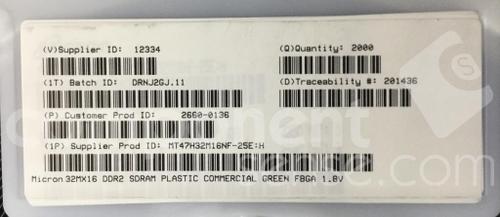

MT47H128M8CF-3IT:H

FBGA 60/128MX8 DDR2 SDRAM PLASTIC PBF FBGA 1.8V

* VDD = 1.8V ±0.1V, VDDQ = 1.8V ±0.1V * JEDEC-standard 1.8V I/O SSTL_18-compatible * Differential data strobe DQS, DQS# option * 4n-bit prefetch architecture * Duplicate output strobe RDQS option for x8 * DLL to align DQ and DQS transitions with CK * 8 internal banks for concurrent operation * Programmable CAS latency CL * Posted CAS additive latency AL * WRITE latency = READ latency - 1 tCK * Selectable burst lengths BL: 4 or 8 * Adjustable data-output drive strength * 64ms, 8192-cycle refresh * On-die termination ODT * Industrial temperature IT option * Automotive temperature AT option * RoHS-compliant * Supports JEDEC clock jitter specification