MAX122BCWG+T

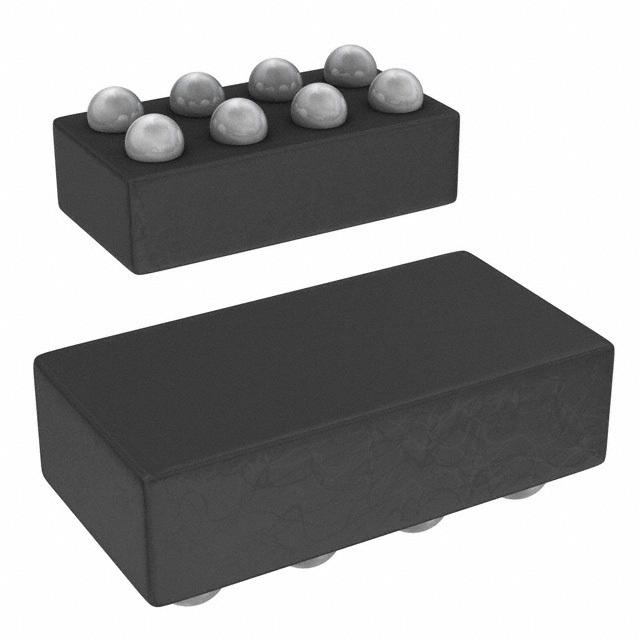

ADC Single SAR 333KSPS 12Bit Parallel 24Pin SOIC W T/R

* 12-Bit Resolution * No Missing Codes Over Temperature * 20ppm/°C -5V Internal Reference * 1.6µs Conversion Time/500ksps Throughput MAX120 * 2.6µs Conversion Time/333ksps Throughput MAX122 * Low Noise and Distortion: * 70dB Minimum SINAD; * -70dB Max THD MAX122 * Low Power Dissipation: 210mW * Separate Track/Hold Control Input * Continuous-Conversion Mode Available * ±5V Input Range, Overvoltage Tolerant to ±15V * 24-Pin Narrow DIP, Wide SO and SSOP Packages

安富利:

The MAX120/MAX122 complete, BiCMOS, sampling 12-bitanalog-to-digital converters ADCs combine an on-chiptrack/hold T/H and a low-drift voltage reference with fastconversion speeds and low-power consumption. The T/H’s350ns acquisition time combined with the MAX120’s 1.6µsconversion time results in throughput rates as high as 500ksamples per second ksps. Throughput rates of 333kspsare possible with the 2.6μs conversion time of the MAX122.The MAX120/MAX122 accept analog input voltages from-5V to +5V. The only external components needed aredecoupling capacitors for the power-supply and referencevoltages. The MAX120 operates with clocks in the0.1MHz to 8MHz frequency range. The MAX122 accepts0.1MHz to 5MHz clock frequencies.The MAX120/MAX122 employ a standard microprocessorµP interface. Three-state data outputs are configuredto operate with 12-bit data buses. Data-access and bus-releasetiming specifications are compatible with mostpopular µPs without resorting to wait states. In addition,the MAX120/MAX122 can interface directly to a first-in,first-out FIFO buffer, virtually eliminating µP interruptoverhead. All logic inputs and outputs are TTL/CMOScompatible. For applications requiring a serial interface,refer to the MAX121.