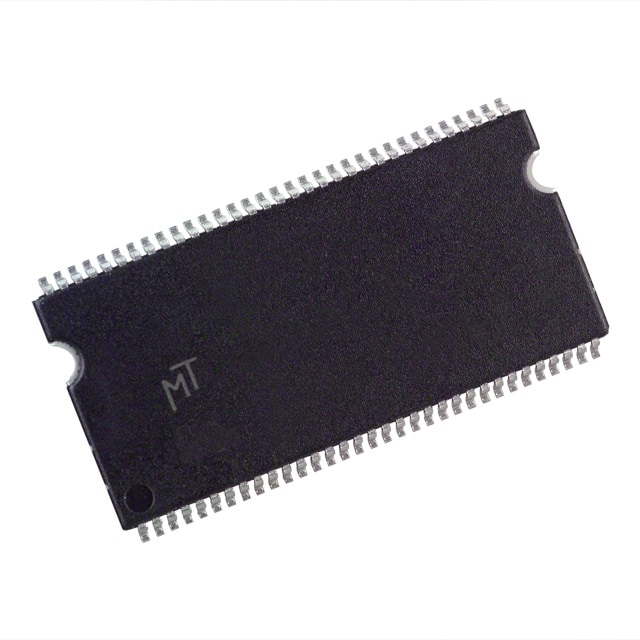

MT46H32M16LFBF-5IT:C

DDR DRAM, 32MX16, 5ns, CMOS, PBGA60, 8 X 9MM, GREEN, PLASTIC, VFBGA-60

* VDD/VDDQ = 1.70–1.95V * 1.2V I/O option VDDQ = 1.14–1.30V * Bidirectional data strobe per byte of data DQS * Internal, pipelined double data rate DDRarchitecture; two data accesses per clock cycle * Differential clock inputs CK and CK# * Commands entered on each positive CK edge * DQS edge-aligned with data for READs; center aligned with data for WRITEs * 4 internal banks for concurrent operation * Data masks DM for masking write data—one mask per byte * Programmable burst lengths BL: 2, 4, 8, or 16 * Concurrent auto precharge option is supported * Auto refresh and self refresh modes * 1.8V LVCMOS-compatible inputs * On-chip temp sensor to control self refresh rate * Partial-array self refresh PASR * Deep power-down DPD * Status read register SRR * Selectable output drive strength DS * Clock stop capability * 64ms refresh