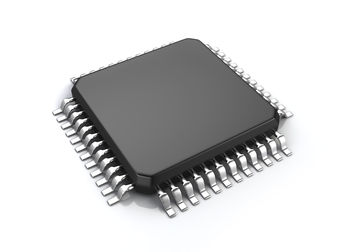

STM8AL3L8ATCX

8位微控制器 -MCU 8 BITS MICROCONTR

The high-density STM8AL3x8x ultra-low-power devices feature an enhanced STM8 CPU core providing increased processing power up to 16 MIPS at 16 MHz while maintaining the advantages of a CISC architecture with improved code density, a 24-bit linear addressing space and an optimized architecture for low-power operations.

The family includes an integrated debug module with a hardware interface SWIM which allows non-intrusive in-application debugging and ultrafast Flash programming.

All high-density STM8AL3x8x microcontrollers feature embedded data EEPROM and low-power low-voltage single-supply program Flash memory.

The devices incorporate an extensive range of enhanced I/Os and peripherals, a 12-bit ADC, two DACs, two comparators, a real-time clock, 8x40 or 4x44-segment LCD, four 16-bit timers, one 8-bit timer, as well as standard communication interfaces such as two SPIs, an I2C interface, and three USARTs. One 8x40 or 4x44-segment LCD is available on the STM8AL3L8x devices. The modular design of the peripheral set allows the same peripherals to be found in different ST microcontroller families including 32-bit families. This makes any transition to a different family very easy, and simplified even more by the use of a common set of development tools.

**Key Features**

- .

- AEC-Q100 grade 1 qualified

- .

- Operating conditions

- .

- Operating power supply range 1.8 V to 3.6 V down to 1.65 V at power down

- .

- Temp. range: -40 to 85 or 125 °C

- .

- Low-power features

- .

- 5 low-power modes: Wait, Low-power run 5.9 µA, Low-power wait 3 µA, Active-halt with full RTC 1.4 µA, Halt 400 nA

- .

- Consumption: 200 µA/MHz+330 µA

- .

- Fast wake up from Halt mode 4.7 µs

- .

- Ultra-low leakage per I/0: 50 nA

- .

- Advanced STM8 core

- .

- Harvard architecture and 3-stage pipeline

- .

- Max freq: 16 MHz, 16 CISC MIPS peak

- .

- Up to 40 external interrupt sources

- .

- Reset and supply management

- .

- Low power, ultra safe BOR reset with 5 programmable thresholds

- .

- Ultra-low-power POR/PDR

- .

- Programmable voltage detector PVD

- .

- Clock management

- .

- 32 kHz and 1-16 MHz crystal oscillators

- .

- Internal 16 MHz factory-trimmed RC and 38 kHz low consumption RC

- .

- Clock security system

- .

- Low-power RTC

- .

- BCD calendar with alarm interrupt,

- .

- Digital calibration with +/- 0.5ppm accuracy

- .

- Advanced anti-tamper detection

- .

- DMA

- .

- 4 ch. for ADC, DACs, SPIs, I2C, USARTs, Timers, 1 ch. for memory-to-memory

- .

- LCD: 8x40 or 4x44 w/ step-up converter

- .

- 12-bit ADC up to 1 Msps / 28 channels,

- .

- Temp. sensor and internal ref. voltage

- .

- Memories

- .

- Up to 64 Kbytes of Flash with up to 2 Kbytes of data EEPROM with ECC and RWW

- .

- Flexible write/read protection modes

- .

- Up to 4 Kbytes of RAM

- .

- 2x12-bit DAC dual mode with output buffer

- .

- 2 ultra-low-power comparators

- .

- 1 with fixed threshold and 1 rail to rail

- .

- Wakeup capability

- .

- Timers

- .

- Three 16-bit timers with 2 channels IC, OC, PWM, quadrature encoder

- .

- One 16-bit advanced control timer with 3 channels, supporting motor control

- .

- One 8-bit timer with 7-bit prescaler

- .

- One window and one independent watchdog

- .

- Beeper timer with 1, 2 or 4 kHz frequencies

- .

- Communication interfaces

- .

- Two synchronous serial interface SPI

- .

- Fast I2C 400 kHz SMBus and PMBus

- .

- Three USARTs IrDA, LIN 1.3, LIN2.0

- .

- Up to 67 I/Os, all mappable on interrupt vectors

- .

- Fast on-chip programming and non-intrusive debugging with SWIM, Bootloader using USART

- .

- 96-bit unique ID