的基本语法:

1:定义一个数据的,定义其位宽和和进制,省略位宽默认32位,省略进制默认十进制,数据之间可以添加下划线

2:X表示不确定的值,Z为高阻态

3:parameter参数类型,可以定义为不变的数据,也可以参数的传递

4:定义字符串时通用C语言的部分字符串,如\n,\t等

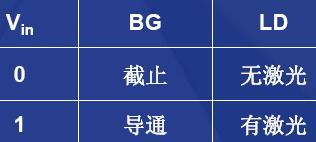

5:变量数据类型主要分为网络类型和寄存器类型。网络类型不能存储数据,寄存器类型可以存储数据。(网络类型:wire和tri主要用作连接单元的连线;Supply0对地建模,supply1对电源建模。Wor和trior实现线或功能;wand和triand实现线与功能;trireg可以存储数值和节点的建模;tri0和tri1用于线逻辑的建模)(寄存器类型:reg型为可定义的无符号整数变量;memory是reg型的一个数组;interger型是32位有符号整数变量)

6:wire型信号可以用于任何方程式的输入,也可作为assign语句或者实例元件的输出。

Reg型数据常用作表示always模块内的自定信号,常代表触发器。

7:逻辑运算符分为数值的与或非也分为按位运算符。

缩减运算符依次高位和地位实现逻辑运算。

关系运算符两个数据进行关系运算,输出真假和不确定X

等式运算符分为逻辑等和严格等。逻辑等输出01X,将X,Z视为不确定的数;关系等分为01,将X,Z视为两种符号。

位拼接运算符将两个数据的某几位拼接在一起

三目运算符相当于if和else,

8:赋值语句分为阻塞赋值和非阻塞赋值

阻塞赋值也就是说它阻塞了其他赋值语句的执行,只能进行一步一步的执行,a=b

非阻塞赋值允许其他verilog语句同时进行操作,a<=b

当使用always时,阻塞赋值来描述组合逻辑,而非阻塞赋值描述时序逻辑。在一个always块中不要同时使用阻塞逻辑和非阻塞逻辑

9:verilog中有01XZ四种逻辑值,逻辑值为1则按照真处理,若为0XZ则按假处理,跳过if中的语句。

在if嵌套中,else总是和它最上面的if来匹配。

Case语句中的case和endcase成对出现。case<