一、实验板电路原理分析

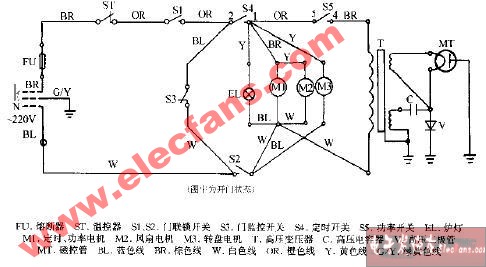

在本制作中,芯片采用EPM7128SLC84-15(公司的MAX7000系列产品),该芯片具有高阻抗、电可擦等特点,可用门单元2500个,有68个I/O引脚、8个逻辑阵列块、128个宏单元,管脚间最大延迟为5ns,工作电压+5V,封装形势为PLCC-84。该实验板的电路如下图所示。

下图中相同标号的线是连接在一起的。Ul为可编程逻辑器件EPM7128S。使用时注意:IO:设置I/O口电压端,可以接3.3V或SV,如果接5V则I/O的输入输出电压为5V,本制作中接5V,在与3.3V系统连接时接3.3V;VCCI:设置内部操作和电压,设置为5v。LK:全局时钟脚,此脚的驱动能力最强,到所有逻辑单元的延时基本相同,所以如果系统有外部时钟输入,建议定义此脚为时钟脚;OEl:全局输出使能,如有三态输出,建议由此脚来控制(也可由内部逻辑产生输出使能信号);GCLRn:全局清零,如有寄存器清零,建议由此脚来控制(也可由内部逻辑产生清零信号);OE2/GCLK2:全局输出使能/全局时钟脚。

SOURE端为+5V的电源端口,在制作时可采用φ4.5的插座或其他方便与身边的+5V电源连接的。C1、CON2、CON3、CON4为可编程逻辑器件I/O口的引出端口,在制作时采用单排针,以便灵活使用外围I/O口设计自己的电路。JTAG接口为5×2的10芯插座,方便与Altera标准的ByteBlasterMV下载线连接。为了做时序电路实验,在板上使用了一个20MHz的有源晶振,用户也可根据自己的需要更换晶振的频率值。

使用有源晶振应注意:有个点标记的为①脚,按逆时针方向(管脚向下)依次为②、③、④脚。其通常的定义为:①脚悬空,②脚接地,③脚接输出,④脚接电源电压。

焊接时,先选一块质量较好的单孔板,在上面规划好各元件和接口插座的布局,然后开始焊接。EPM7128S放在PLCC-84插座上,芯片缺口对准插座缺口,PLCC-84插座引脚排列如右图所示。

晶振应尽可能靠近GCLK脚。在板上的+5V走线与地之间应在一定的距离,并接一只104的退耦电容。

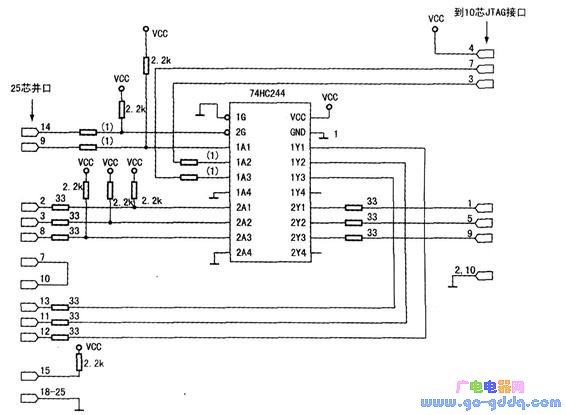

三、下载线的制作

EPM7128的下载线为ByteBlasterMV并口下载线,可以对MAX9000MAX7000SMAX7000B、MAX7000A、MAX3000系列器件进行下载。也可以配置APEX20K,FLEX10K(包含FLEX10KAandFLEX10KE),、FLEX8000和FLEX6000器件。下图为Altera提供的ByteBlasterMV下载线电路图。

-电子元器件采购网(www.ruidan.com)是本土元器件目录分销商,采用“小批量、现货、样品”销售模式,致力于满足客户多型号、高质量、快速交付的采购需求。 自建高效智能仓储,拥有自营库存超过50,000种,提供一站式正品现货采购、个性化解决方案、选型替代等多元化服务。