HDLBits FSM

时间:2023-12-06 10:07:01

Rule90

module top_module( input clk, input load, input [511:0] data, output [511:0] q ); always@(posedge clk) begin if(load) q <= data; else q <= {

1'b0,q[511:1]} ^ {q[510:0],1'b0};//右移或左移 end endmodule Rule110

module top_module( input clk, input load, input [511:0] data, output [511:0] q ); always@(posedge clk)begin if(load)begin q <= data; end else begin q <= ~((~q & ~{

q[510:0],1'b0}) | (q & {q[510:0],1'b0} & {

1'b0,q[511:1]})); end end endmodule Conwaylife

这个生命游戏暂时不懂,以后再做

simple FSM1

module top_module( input clk, input areset, // Asynchronous reset to state B input in, output out);//

parameter A=0, B=1;

reg state, next_state;

always@(posedge clk or posedge areset)

begin

if(areset)

state <= B;

else

state <= next_state;

end

always@(*)

begin

case(state)

B: next_state = in ? B : A;

A: next_state = in ? A : B;

default: next_state = B;

endcase

end

assign out = state==B ? 1 : 0;

endmodule

后面几个和这个是类似的,就不重复写 了

Fsm3comb

module top_module(

input in,

input [1:0] state,

output [1:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

always@(*)

begin

case(state)

A: next_state = in ? B : A;

B: next_state = in ? B : C;

C: next_state = in ? D : A;

D: next_state = in ? B : C;

default: next_state = A;

endcase

end

assign out = state==D ? 1'b1 : 1'b0;

endmodule

Fsm3-onehot

module top_module(

input in,

input [3:0] state,

output [3:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

//用独热码写状态机,只关注其中一位的变化

// State transition logic: Derive an equation for each state flip-flop.

assign next_state[A] = state[A] & (~in) | state[C] & (~in);

assign next_state[B] = state[A] & in | state[B] & in | state[D] & in;

assign next_state[C] = state[B] & ~in | state[D] & ~in;

assign next_state[D] = state[C] & in;

// Output logic:

assign out = state[D];

endmodule

Design a moor FSM(Exams/ece241 2013 q4)

一开始没有搞懂题的意思是什么。搞懂意思才能知道状态转化

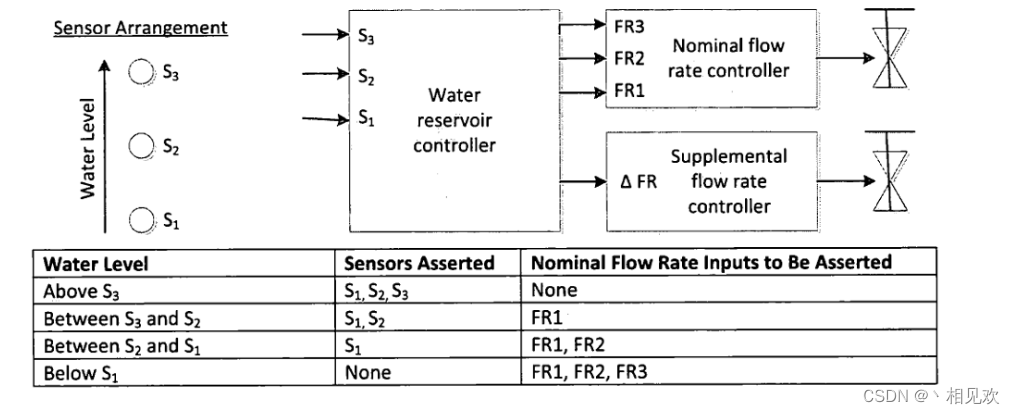

大概可以这么理解一下,有一个水池a,有s1,s2,s3三个传感器作为输入信号,用来指示水位的高低。然后有两个输出信号,相当于两个水池b,c,水位不足时,要从这两个水池向原来的水池a加水,然后根据传感器的状态不同,选择是从b和c哪一个水池向a水池加。

根据图表,可知状态变化。s[3:1]=000,001,011,111对应的输出会发生变化。

module top_module (

input clk,

input reset,

input [3:1] s,

output fr3,

output fr2,

output fr1,

output dfr

);

reg [2:0] cs,ns;

parameter idle = 3'd0;

parameter s1 = 3'd1;

parameter s2 = 3'd2;

parameter s3 = 3'd3;

always@(posedge clk)

begin

if(reset)

cs <= idle;

else

cs <= ns;

end

always@(*)

begin

case(cs)

idle:begin

case(s)

3'b001: ns = s1;

3'b011: ns = s2;

3'b111: ns = s3;

default: ns = idle;

endcase

end

s1:begin

case(s)

3'b001: ns = s1;

3'b011: ns = s2;

3'b111: ns = s3;

default: ns = idle;

endcase

end

s2:begin

case(s)

3'b001: ns = s1;

3'b011: ns = s2;

3'b111: ns = s3;

default: ns = idle;

endcase

end

s3:begin

case(s)

3'b001: ns = s1;

3'b011: ns = s2;

3'b111: ns = s3;

default: ns = idle;

endcase

end

default: ns = idle;

endcase

end

assign fr3 = cs==idle ? 1'b1 : 1'b0;

assign fr2 = (cs==idle || cs==s1) ? 1'b1 : 1'b0;

assign fr1 = (cs==idle || cs==s1 || cs==s2) ? 1'b1 : 1'b0;

//当前时刻水位与前一刻水位的高低决定dfr

//前一时刻低于当前,为0;反之为1

reg fr1_reg,fr2_reg,fr3_reg;

always@(posedge clk)

begin

fr1_reg <= fr1;

fr2_reg <= fr2;

fr3_reg <= fr3;

end

always@(*)

begin

if(~fr3 & fr3_reg | ~fr2 & fr2_reg | ~fr1 & fr1_reg)

dfr = 1'b0;

else if(fr3 & ~fr3_reg | fr2 & ~fr2_reg | fr1 & ~fr1_reg)

dfr = 1'b1;

end

endmodule

lemmings1

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

output walk_left,

output walk_right); //

// parameter LEFT=0, RIGHT=1, ...

reg state, next_state;

parameter left = 0;

parameter right = 1;

always@(posedge clk or posedge areset)

begin

if(areset)

state <= left;

else

state <= next_state;

end

always@(*)

begin

case(state)

left: next_state = bump_left ? right : left;

right: next_state = bump_right ? left : right;

default: next_state = left;

endcase

end

assign walk_left = state==left;

assign walk_right = state==right;

endmodule

lemmings2

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

output walk_left,

output walk_right,

output aaah );

// parameter LEFT=0, RIGHT=1, ...

reg [1:0]state, next_state;

parameter left = 2'd0;

parameter right = 2'd1;

parameter g_left = 2'd2;

parameter g_right = 2'd3;

always@(posedge clk or posedge areset)

begin

if(areset)

state <= left;

else

state <= next_state;

end

always@(*)

begin

case(state)

left: next_state = ground ? (bump_left ? right : left) : g_left;

right: next_state = ground ? (bump_right ? left : right) : g_right;

g_left: next_state = ground ? left : g_left;

g_right: next_state = ground ? right : g_right;

default: next_state = left;

endcase

end

assign walk_left = state==left;

assign walk_right = state==right;

assign aaah = state==g_left || state==g_right;

endmodule

lemmings3

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

input dig,

output walk_left,

output walk_right,

output aaah,

output digging );

//定义状态,fall优先级最高,其次为dig,最后为切换方向

parameter left = 0;

parameter right = 1;

parameter fall_left = 2;

parameter fall_right = 3;

parameter dig_left = 4;

parameter dig_right = 5;

reg [2:0] cs,ns;

always@(posedge clk or posedge areset)

begin

if(areset)

cs <= left;

else

cs <= ns;

end

always@(*)

begin

case(cs)

left: ns = ground ? (dig ? dig_left : (bump_left ? right : left)) : fall_left;

right: ns = ground ? (dig ? dig_right : (bump_right ? left : right)) : fall_right;

fall_left: ns = ground ? left : fall_left;

fall_right: ns = ground ? right : fall_right;

dig_left: ns = ground ? dig_left : fall_left;

dig_right: ns = ground ? dig_right : fall_right;

default: ns = left;

endcase

end

assign walk_left = (cs==left) ? 1'b1 : 1'b0;

assign walk_right = (cs==right) ? 1'b1 : 1'b0;

assign aaah = (cs==fall_left || cs==fall_right) ? 1'b1 : 1'b0;

assign digging = (cs==dig_left || cs==dig_right) ? 1'b1 : 1'b0;

endmodule

lemmings4

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

input dig,

output walk_left,

output walk_right,

output aaah,

output digging );

//定义状态,fall优先级最高,其次为dig,最后为切换方向

parameter left = 0;

parameter right = 1;

parameter fall_left = 2;

parameter fall_right = 3;

parameter dig_left = 4;

parameter dig_right = 5;

parameter splatter = 6;

parameter act_end = 7;

//如果下降超过20个时钟,那lemmings就会死亡、输出为0,直到复位

//可以定义一个计数器。进行计时

reg [2:0] cs,ns;

reg [4:0] cnt;

always@(posedge clk)

begin

if(areset)

cnt <= 5'd0;

else if(ns==fall_left || ns==fall_right)

cnt <= cnt+1'b1;

else

cnt <= 5'd0;

end

always@(posedge clk or posedge areset)

begin

if(areset)

cs <= left;

else

cs <= ns;

end

always@(*)

begin

case(cs)

left: ns = ground ? (dig ? dig_left : (bump_left ? right : left)) : fall_left;

right: ns = ground ? (dig ? dig_right : (bump_right ? left : right)) : fall_right;

fall_left: ns = ground ? left : (cnt>5'd19 ? splatter : fall_left);

fall_right: ns = ground ? right : (cnt>5'd19 ? splatter : fall_right);

dig_left: ns = ground ? dig_left : fall_left;

dig_right: ns = ground ? dig_right : fall_right;

splatter: ns = ground ? act_end : splatter;

act_end: ns = act_end;

default: ns = left;

endcase

end

assign walk_left = (cs==left) ? 1'b1 : 1'b0;

assign walk_right = (cs==right) ? 1'b1 : 1'b0;

assign aaah = (cs==fall_left || cs==fall_right || cs==splatter) ? 1'b1 : 1'b0;

assign digging = (cs==dig_left || cs==dig_right) ? 1'b1 : 1'b0;

endmodule

FSM one-hot

module top_module(

input in,

input [9:0] state,

output [9:0] next_state,

output out1,

output out2);

//和状态机关系不大。没必要按照状态机写

assign next_state[0] = ~in & (state[0] | state[1] | state[2] | state[3] | state[4] | state[7] | state[8] | state[9]);

assign next_state[1] = in & (state[0] | state[8] | state[9]);

assign next_state[2] = in & state[1];

assign next_state[3] = in & state[2];

assign next_state[4] = in & state[3];

assign next_state[5] = in & state[4];

assign next_state[6] = in & state[5];

assign next_state[7] = in & (state[6] | state[7]);

assign next_state[8] = ~in & state[5];

assign next_state[9] = ~in & state[6];

assign out1 = state[8] | state[9];

assign out2 = state[7] | state[9];

endmodule

FSM ps2

module top_module(

input clk,

input [7:0] in,

input reset, // Synchronous reset

output done); //

parameter s0 = 2'd0;

parameter s1 = 2'd1;

parameter s2 = 2'd2;

parameter s3 = 2'd3;

reg[1:0] cs,ns;

//如果输入数据的第三位为1,指示接收数据的开始,然后3字节后完成

always@(posedge clk)

begin

if(reset)

cs <= s0;

else

cs <= ns;

end

always@(*)

begin

case(cs)

s0: ns = in[3] ? s1 : s0;

s1: ns = s2;

s2: ns = s3;

s3: ns = in[3] ? s1 : s0;

default: ns = s0;

endcase

end

assign done = cs==s3 ? 1'b1 : 1'b0;

endmodule

FSM ps2data

module top_module( input clk, input [7:0] in, input reset, // Synchronous reset output [23:0] out_bytes, output done); // parameter s0 = 2'd0; parameter s1 = 2'd1; parameter s2 = 2'd2; parameter s3 = 2'd3; reg[1:0] cs,ns; reg[23:0] out_bytes_reg; //如果输入数据的第三位为1,指示接收数据的开始,然后3字节后完成 always@(posedge clk) begin if(reset) cs <= s0; else cs <= ns; end always@(*) begin case(cs) s0: ns = in[3] ? s1 : s0; s1: ns = s2; s2: ns = s3; s3: ns = in[元器件数据手册、IC替代型号,打造电子元器件IC百科大全!