数电实验四-触发器(Multisim和Basys3)

时间:2023-09-08 08:07:00

微信微信官方账号:创享日记(或csds992022)

发送: 触发器

免费获得完整的无水印实验报告

一、实验目的

1.学习触发器逻辑功能的测试方法。

2、熟悉基本RS触发器的组成、工作原理和性能。

3、熟悉集成JK触发器和集成D触发器的逻辑功能成D触发器。

二、实验仪器设备

1.数字电路实验箱

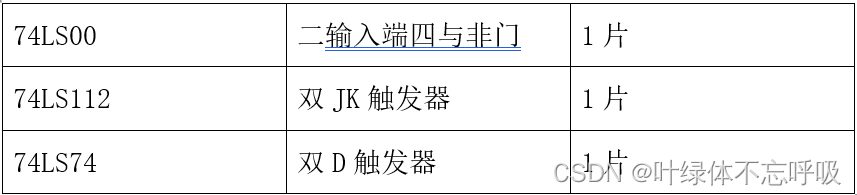

2.器材

三、实验内容及步骤

1.基本RS触发器逻辑功能的测试

基本RS如图4-1-1所示,触发器由两个与非门首相连接组成。

图中,Rd’和Sd输入端接逻辑电平开关,Q和Q输出端接电平显示器。

(1)按表4-1-1的要求给出Rd’、Sd借助电平显示器观察和记录端加信号Q将结果记录在表4-1-1中。

(2)不定状态试验

连接Rd’和Sd接收相同的逻辑电平开关。首先,开关打开到L”,即Rd’=Sd’=0.当逻辑电平开关由L”变为“H”时,即Rd’=Sd’=1.观察触发器Q的状态,做5~分析结果10次以上,体验不确定的含义。

2、集成JK触发器逻辑功能的测试

JK触发器是一种下降边缘触发器,其逻辑符号如图4-2-1所示。LS112芯片是双JK集成触发器电路器电路,如图4-2-1所示JK触发器。图4-2-2是74LS112实验箱面板上的逻辑接线图。

(1)测试异步位置和复位功能

如图4-2-3所示,J、K和CP任意状态(实验时一般悬空),Sa 是位置端,是的Rs复位端。Sd’和Rd接逻辑电平开关,Q和Q按表4-2-1测试Q端状态,将结果填入表4-2-1。 X表示任意状态。

(2)逻辑功能的测试(J、 K与(Q^(n 1)关系)

a)按图4-2-4接线,先将触发器1设置为触发器 仪器的初始状态为1,即Q=1。

①触发器1时,Rd’=1,Sd’=0。

②触发器置“1”完成后,Rd’=1, Sd’=1。

从CP端输入单脉冲(从实验箱面板上获取)。Q端状态按表4-2-2测量,结果填入表4-2-2。

注意观察: i)触发器状态及J、K关系。

ii)触发器触发时钟脉冲的上升或下降。

注:表中↑是CP的上升边沿,↓是为CP下升边缘。

b)将JK接成计数状态的触发器(JK触发器转换成T’触发器)

J=1, K=1,Rd’=1,Sd’=1。

(略)

前几天发现了一个很好的人工智能学习网站,通俗易懂,幽默幽默,没有广告,可以自己看看。(点击跳转人工智能学习资料)