微电子电路——期末总结

时间:2023-08-16 17:07:00

这是我对微电子电路期中考试的总结,涵盖了《大规模集成电路原理与设计》前三章,比较详细,仅供参考。

关于例题,你可以看看我的另一个博客微电子电路-例题总结

一、绪论

1、时间轴:

第一台计算机诞生于1946年(bell lab)

1947年晶体管发面取代电子管

第一个半导体集成电路诞生于1958年(TI实验室)

单片集成电路1959硅平面工艺

1960第一个mos管诞生

1963pmos与nmos互补mos诞生(cmos)

1970DRAM动态随机存储器诞生

1971微处理器诞生

2、摩尔定律:晶体管集成度每18个月翻一番,即Area(0.5)=L(0.7)W(0.7)

3.等比缩小原则:恒定电场等比缩小原则、恒定电压等比缩小原则和准恒定电场等比缩小原则

硅集成电路分类:双极性(同时使用电子和空穴,分为饱和和和和非饱和);mos型(用mos晶体管,分nmos电子导电,一端接地和pmos穴位导电,一端接VDD)

5.集成电路分类:

工作特点:数字集成电路、模拟集成电路和数模模数转换电路

可分为通用集成电路和专用集成电路(只要不是CPU都是)

6.生产工艺:砂采集-硅熔炼-单晶硅棒-硅棒切割-晶圆抛光-涂光刻胶-光刻(一个晶圆可以切割数百个处理器,其中晶体管是开关,控制芯片内的电流方向)-溶解光刻胶-蚀刻(部分未被光刻胶腐蚀)-离子注入-去除光刻胶-晶体管完成-晶圆试验-晶圆切片-封装-等级试验

二、基本元件

本征半导体:无杂质,纯度高,具有晶体结构的半导体,电子和空穴成对出现,称为电子-空穴对。不断产生电子和空穴,形成动态平衡,称为载流子。其浓度与温度密切相关。

2、施主杂质:向硅半导体提供一个自由电子而本身带正电的粒子杂质,此时电子为多数载流子,称为n型半导体。

3.主要杂质:向硅半导体提供空穴和负杂质,主要依靠受主提供空穴导电,称为p型半导体的空穴为大多数载流子。

4.杂质浓度决定多子浓度,温度决定少子浓度(来自本征半导体)。一般来说,它是电中性的,因为它是电中性的。

5、PN结:n类型与p型半导体的交界面。

扩散运动:因为PN载流子浓度梯度存在于结界面,导致多子电子从N到P,空穴由P到N,多子运动导致N型施主离子(正)和P型受主离子(负)形成电场,阻碍扩散运动,直到中间形成耗尽层。

7.漂移:由于上述电场的存在,少子漂移,即电子从P到PN,空穴从N到P,与扩散运动相反。

当两者动态平衡时,扩散运动使扩散电流逐渐减小,漂移运动逐渐增加,PN总电流为0,空间电荷区宽度稳定

9、外加正向电压的时候(P正N负),正电流外电场与内电场方向相反,阻碍减弱,扩散运动继续,净正电流为导通;加上反向电压(P负N正),外电场和内电场方向相同,更阻碍,使空间电荷区变宽,产生反向电流,表现为不导通。这就是单向导电的原因

10、MOS结构:在(PMOS)加电压后,栅极和衬底可以有四种变化:

①积累态:栅负底正,即VG<0.栅极充满电子,空穴被吸引到表面形成积累层

②耗尽态:VG>0.栅极产生少量正电荷,空穴被派出,形成耗尽层

③反型态:VG随着数量的增加,山鸡有更多的正电荷,少量的电子进入表面形成反形层,允许电流通过

④强反型态:VG增加,使表面少子浓度超过多子,反型层电子限制在沟内,P型沟由电子组成,运行电流通过

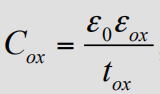

格栅氧化层单位面积电容为:

其中ε介电常数和相对介电常数,tox格栅氧化层厚度

同样,耗尽层的单位面积电容器为:

其中xd衬底厚度,或耗尽层厚度

11、nmos:PN型源泄漏型衬底S、栅G、源D、底B,当VG=0时无沟通不导通,0时无沟通不导通VG>VT(阈值电压)泄漏与源之间有电流,电压为泄漏高源低,阈值电压为正值;若为耗尽型,则在VG=0时有电流,否则无电流,一般不考虑。阈值电压为负值。

随着栅源电压VGS增加和泄漏电压VDS依次增加

截止区(VGS

也可以写:

饱和区(VGS>VT且VDS>VGS-VT),电流达到饱和值

12、pmos:NP型衬底源泄漏S、栅G、源D、底B,当VG=0时无沟通不导通,0时无沟通不导通VG

网源电压VGS降低和泄漏电压VDS依次减少

截止区(VGS>VT),此时电流为0

线性区(VGS

也可以写:

饱和区(VGS

13、阈值电压VT:当达到强反形成沟时,所需的格栅压力VG。γ体效应系数

其中VT0为衬底偏压为0,即VBS=阈值电压电压

如果这个,一定要带计算器!

14、亚阈值电流:当VG小于VT但大于0的时候(nmos),没有导电沟,但少子使漏电流ID不是0流子为少子,主要是扩散运动,计算公式为:

I0为VG=VT随着时间的电流VGS当漏源电压变化时,成指数变化>3kT/q亚阈值电流与泄漏电流基本无关。亚阈值电流受温度影响很大。

15、mos瞬态特性:

本征电容:栅极与源极、栅极与漏极、栅极与衬底之间的电容,

当VGS

随着VDS的增大,CGD减小,CGS增大,当VDS=VGS-VT这时,沟道在漏端发生断,此时CGD减小到0,而CGS增到最大

而对于CGB,达到强反型后为0,以前有一定的变化趋势。

覆盖电容:网格极与源极、网格极与漏极之间有一定的覆盖区域,有电容

因此,总格栅源电容和格栅泄漏电容为:

PN结电容:在泄漏和衬底之间形成PN结,会有两个电容器,只有两个电容器VS和VD与电压有关,可有公式:

其中AS、AD和PS、PD分别是源漏区的面积和周长,CjA单位面积pn底部电容,CjP是单位周长的pn结侧壁电容:

Cj0和Cjp零偏压时单位面积底部结电容和单位长度侧壁结电容

xj是源,漏区深度

16.电容器:只要有两个公式:

电容器的近似公式:

电容与温度公式:

17.电阻:记住条形电阻和电阻和温度的公式:

三、反相器

1、cmos反相器结构:

反相器是一个nmos与一个pmos连接,其中栅极连接,为输入端;漏极连接,为输出端。pmos源极与衬底接高电平,nmos低电平的源极和衬底。

当输入为高电平时,是的pmos而言,Vgs=0;对nmos而言,Vgs=VDD因此,高电平相当于pmos截止,nmos导通相当于放电,对外显示低电平0;当输入为低电平时,对pmos而言,Vgs=-VDD对nmos而言,Vgs=0低电平相当于nmos截止,pmos导通,相当于充电,对外显示高电平1。

2.直流特性:

输入电压为0~VDD之间时,由于nmos与pmos因此,在稳定状态下流过两者的电流必然相等,即IDN=IDP。

由于连接方式,决定了以下关系:

VGSN=Vin,VDSN=Vout

VGSP=Vin-VDD,VDSP=Vout-VDD

根据不同线性区域和饱和区域的电压,可以绘制7个不同的区域,如下:

当 0≤Vin≤VTN,NMOS截止, PMOS线性,Vin在一定范围变化(0~VTN), Vout始终保持VDD。

当VTN

当 Vout+VTP≤Vin≤Vout+VTN,NMOS饱和, PMOS饱和,VTC垂直下降,此时电流最大。

当Vout+VTN

当VDD≥Vin≥VDD+VTP,NMOS线性, PMOS截止,Vin在一定范围变化(VDD+VTP ~ VDD), Vout始终保持0

理想VTC曲线:

(1)为输出高电平区

(2)、(3)、(4)为转变区

(5)为输出低电平区

其中(3)表现为垂线段

3、空穴迁移率约为电子的40%

4、直流噪声容限:允许的输入电平变化范围,在图上表示为斜率为-1的切线的切点的坐标

5、最大噪声容限:VNLM=Vit-0=Vit,VNHM=VDD-Vit,求其中最小值

6、在测试直流特性的时候,需要在vout处加上一个电容

7、负载电容:分三部分,即两个mos管的漏底电容CDBN和CDBP,互联线引起的电容CI和下级电路的输入电容Cin,最终可计算出公式为:

而面对级联电路,此时的Cin为全部的mos的栅电容构成,N为扇出系数

8、上升时间:输出电压从V10%上升到V90%的时间,tr表示:

9、下降时间:输出电压从V90%下降到V10%的时间,tf表示

10、上升延迟时间:输出信号下降到V50%的时间减去输入信号上升到V50%的时间,tpLH表示,计算式为:

其中CL为负载电容,题目中给出

11、下降延迟时间:输出信号上升到V50%的时间减去输入信号下降到V50%的时间,tpHL表示,计算式为:

其中CL为负载电容,题目中给出

12、平均延迟时间:上升延迟时间+下降延迟时间/2

如果要求是精确设计,可以通过如下公式:

参考值(W/L, CLref, tPref)

新的条件:C’L, t’P

设计:(W/L)’

13、MOS工艺中,将最小晶体管尺寸设为(W/L)=2/1

14、必须维持输入信号的时间大于电路的延迟时间

15、反相器级联的时候,会有:

f为环形振荡器电路的工作频率,tp为延迟时间,n为反相器级数(奇数)

16、最优化设计:全对称设计

VTN=-VTP,KN=KP

此时为了使K相等,会有LP=LN,WP=2.5WN

此时逻辑阈值、噪声容限、上升下降时间为

Vit=1/2VDD

VNLM=VNHM=1/2VDD

TPLH=TPHL

tr=tf

四、基本单元电路

1、两输入与非门结构特点:

由于pmos是低电平导通,相当于0到1;nmos是高电平导通,相当于1到0,所以可以认为,pmos是处理当输入为0的时候的上拉电路,而nmos是处理输入为1的时候的下拉电路,具体情况如下:

①两个pmos串联,相当于两个均为0的时候才输出1

②两个pmos并联,相当于任何一个为0的时候就输出1

③两个nmos串联,相当于两个均为1的时候才输出0

④两个nmos并联,相当于任意一个为1的时候就输出0

门电路便是通过这个原理实现的

2、与非门:

由真值表可以看出来,输出为1的情况有三个,即AB中任意一个为0的时候就会输出1,表示AB的两个pmos是并联的;同理,输出为0的情况只有一个,即AB必须同时为1的时候才输出0,表示AB两个的nmos是串联的,由此得到:

3、或非门:

由真值表可以看出来,输出为1的情况有一个,即AB同时为0时会输出1,表示AB的两个pmos是串联的;同理,输出为0的情况有三个,即AB任一个为1的时候输出0,表示AB两个的nmos是并联的,由此得到:

4、复杂逻辑门电路:

在处理复杂逻辑门电路的时候,可以分上拉电路和下拉电路来分别进行处理,这个时候,由于nmos只能够输出0,所以是下拉电路,处理的是表达式所有输出0的情况;而pmos智能输出1,所以是上拉电路,处理的是表达式所有输出为1的情况,可以认为:

如

nmos处理的是为0的情况,即取反后为一的情况:

可以看出来,A和B是并联的 ,然后结果与C串联,再与D并联,由此可以得到下拉电路:

两个接口,任意一个接地,另一个为输出。

同理,对pmos构成的上拉电路,处理的是为1的情况,我们需要将他化为和之积的情况,并且将所有的字母都变为取反的形式,如:

之所以需要将所有的字母变为取反的形式,是因为pmos处理的是输入为0的情况。由此我们可以看出来,A和B先串联,然后和C并联,最后与D串联,由此得到:

其中任意一个端口接高电平,另一个为输出。

5、每个输入同时接一个NMOS管和一个PMOS管的栅极,n个输入时,共有2n个MOS管

6、实现不带“非”的逻辑功能需要用互补CMOS门加一个反相器,或者是两级互补CMOS

7、对于两个mos管串联的情况,通过两个mos管的电流与通过其中任意一个mos管的电流是一样的,而又因为mos管工作的时候处于饱和区,由此可以列出如下等式,其中VX为两mos管交界处的电压:

最终计算出来的等效的Keff值有如下关系(宽长比同理):

8、对两个mos管并联的情况,通过两个mos管的电流是通过其中任意一个mos管的电流的和,因为处于饱和区,所以可以有如下等式:

最终计算出来的等效Keff值为两个K的和(宽长比同理):

9、等效反相器:将我们的上拉电路看做一个pmos,下拉电路看做一个nmos,此时整个电路被看做了一个简单的反相器,此时,便可以计算出与反相器一样的上升时间,下降时间,上升延迟,下降延迟,平均延迟以及Vit

10、最坏情况:上升时只有一个pmos管充电,下降时所有串联nmos放电,以与非门为例,此时有:

这是因为,上拉电路中等效的K值中,只有一个pmos是有效的;而对下拉电路的等效K值,所有串联的nmos都是有效的,此时K=KN/n,会变得相当小。由于要使上升延迟与下降延迟时间相等,将会对宽长比要求更高。

11、面积:宽*长的和

12、每增加一个输入变量,增加两个晶体管

13、用mos管实现传输门,类似于开关有两种方式:

①单mos管

②cmos传输门

14、单MOS管:开关闭合时,根据上级电路的输出对电容充放电,做为下级电路的输入。单管MOS断开时,下级输入不确定

nmos:

①双向导通

②当开关(栅极)为0的时候,下级电路输入不确定

③当上级输入为高电平的时候,下级电路实际输入为VDD-VTN

④当上级输入为低电平的时候,下级电路实际输入为0V

pmos:

①双向导通

②当开关(栅极)为0的时候,下级电路输入不确定

③当上级输入为高电平的时候,下级电路实际输入为VDD

④当上级输入为低电平的时候,下级电路实际输入为|VTP|

15、CMOS传输门:需要一对互补的控制信号,VC=VDD时,NMOS和PMOS都导通,CMOS传输门导通

16、动态cmos电路:由于我们的下拉电路取0的时候,只要上拉电路输出1,我们就可以实现一个门电路,于是就有了动态cmos电路:

下拉网络:逻辑块&增加 MN

上拉网络:MP

MN和MP受同一时钟控制, 上、下拉网络不会同时导通

每次需要一个时钟周期,分别作了预充与求值两件事:

①φ=0:

预充,MP将CL充电至VDD

②φ=1

求值,NMOS逻辑块决定下拉网络是否导通

下拉导通,CL放电至0V

下拉关闭,CL保持预充高电平

此时有:

17、比较:

①静态cmos:只要不断电,输出信息可以长久保持

②动态cmos:需要预充和求值:

预冲:利用电容的存储效应来预冲(一定时间段保持)

求值:只需要考虑下拉电路导通时的时延

优点:减小面积、提高速度

18、动态多米诺cmos电路:是一个级联电路,基于单一时钟,预充+求值两个过程。需要在级联之间加反相器。

五、数字集成电路子系统设计

1、随机存储器RAM:分静态存储器SRAM(cache)与动态存储器DRAM(内存)。

2、SRAM单元:

实际上就是两个反相器的交叉耦合:

以上中,BL和BL!分别是输入或输出数据的正值与反值。同理,D和D!分别是存储数据的正值与反值

读操作:假设D=0

①预充阶段:此时位线BL和BL!由敏感放大器电路充至 1/2 VDD;字线WL=0,传输开关M5和M6截止

②传输开关打开:此时字线WL=1

③读数据:M5导通,电流 i1 从 BL 流进,M6导通,电流 i2 流出到 BL!,敏感放大器迅速呈现和存储数据一样的状态

为了让数据不受干扰,保证:

①D处电压 < M3阈值电压

②D!处电压 > VDD - |VTP|,保持M2截止

最终,如图所示,BL为0,BL!为1:

写操作:位线将被写入单元中的数据初始化,BL = Data, BL! = Data!

字线WL=VDD,开关导通

充放电写入数据

3、DRAM单元:

只需要一个晶体管和一个电容器可以实现存储1bit。用电容取代双稳态电路,相当于用电容的电压来存储数据,因泄漏电流,电容信息会衰减,所以需要定时刷新。使用nmos当选中开关。

写操作:BL为待写入数据,WL为高电平,这个时候,如果输入为0,电容放电,存储逻辑0;若输入为1,电容充电,存储逻辑1,但不一定能够到达高电平,只能达到VG-VTN(开关的限定)

读操作:位线预充,字线选中,mos管导通,这个时候CBL和CC电荷共享,位线电压稍微发生变化,位线电压改变的幅度和极性符号与存储信息有关:

4、地址译码器:

具体情况如下:

其存储打开之后,可以看到是这么的一个情况:

在其中,接入了nmos管的是0,没有的是1

5、敏感放大器:主要有差分感应放大器和预充电电路两个部分。

读操作(加上敏感放大器):

①预冲:φP升高,激活预充电电路,位线BL和BL!电压相等,φP降低

②位线电压差:字线WL升高,存储单元与位线BL和BL!相连,BL和BL!产生电压差

③敏感放大器工作:φS升高,放大器根据电压差,正反馈

6、ROM:只读存储器,断电后,信息不丢失;写:可编程ROM,如下所示,和地址译码器很像:

7、D锁存器:

当C=1,传输门1导通,传输门2截止;数据D传入更新Q、Q!

当C=0,传输门1截止,传输门2导通;Q和Q!保持

8、RS触发器:

R=1 & S=1,Q和Q!都为0,然而若R、S同时返回0,则输出不确定,即如图:

9、D触发器用于时序逻辑,如寄存器(级联电路,需要考虑同步);D锁存器用于组合逻辑(不需要考虑同步)

10、指令执行过程:

①取指令:程序计数器(PC)->待执行指令的位置,根据PC读出指令,送到IR

②指令译码:指令译码逻辑翻译指令信息(指令的类型、操作、操作数或操作数地址、计算结果的地址),产生对应的控制信号

③取操作数:CPU按照指令译码阶段提取出来的地址,取出操作数送到ALU等运算器

④执行过程:运算器中的算术逻辑单元、移位器、乘法器等模块,对取来的操作数进行运算

⑤存运算结果:指令执行后的结果,根据指令要求,存到寄存器或存储器中

11、1位全加器:

公式如下:

真值表如下:

12、行波进位加法器:

进位产生信号G,进位传递信号P

13、超前进位加法器:

公式如下:

假设n位加法器可以分为k组,每组4位。则其中一组的进位输出逻辑可以表示为:

每组可以并行运算GG和GP,经过一级逻辑门就可以得到组进位输出信号。