射频微波芯片设计2:滤波器芯片

时间:2023-06-30 16:07:00

《射频微波芯片设计》专栏适用于具有一定微波基础知识的大学生、在职射频工程师、大学研究所研究人员,掌握从射频到毫米波的芯片设计流程、设计方法、设计要点和最新的射频/毫米波前端芯片工程实现技术。

本文分为四部分:讨论为什么要做滤波器、基本概念-什么是滤波器?、滤波器设计理论-分析底层数学逻辑以及芯片滤波器的设计——实际工程怎么做滤波器芯片。(全文阅读大约需要5分钟。如果你能冷静下来阅读超过10分钟,自由设计滤波器,并帮助我表扬和分享,这将是我一个字一个字地码这篇文章的最大荣幸)

前言

相信做射频微波的的学生对滤波器这个术语并不陌生。这可能是学习微波网络的经典案例分析设备。本文还将以带滤波器芯片的工程实例出发,带您进入RFIC/MMIC从芯片设计的角度思考大门RFIC/MMIC设计。

学生们可能会问,既然滤波器的理论和设计过程如此完美,我们只需要了解一些指标知识,然后购买成熟的产品,为什么要花很多精力去学习呢?在这方面,作者认为,虽然滤波器设计理论已经成熟和研究和发展多年,但根据近年来的供需关系,我们的工程师应该注意:

1.滤波器市场巨大

智研咨询发布的《2021-2027年中国滤波器行业市场运行格局及投资前景分析报告》数据显示,2020年全球智能手机出货量为12.同比下降592亿部.8%;2021年第一季度全球智能手机出货量为3.46亿部。

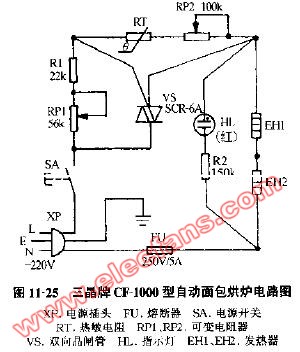

2015-2021年第一季度全球智能手机出货量

资料来源:IDC、智研咨询整理

滤波器是射频前端芯片中价值最高的细分领域,增长最快。滤波器占53%。

射频前端价值分布

资料来源:Yole、智研咨询整理

2015-2020年全球滤波器市场规模

资料来源:Yole、智研咨询整理

2.摩尔定律的发展间接促进了小型化、低成本、高性能滤波器的发展

根据新材料、新工艺的不断发展IEEE和IET期刊论文的研究发现,过滤器的研究存在两极分化的研究趋势,一是利用各种酷的数学公式推导出各种传输零极点,然后实现复杂的过滤器,另一种是新材料、新工艺的过滤器研究。对于简单、实用、低成本、高性能的过滤器研究,主要在专利中可见。

作者认为,他对滤波器的后续研究大致可以分为三个方向:

一是研究高性能全可调(可重构)滤波器,实现多系统、多场景复用功能;

二是对于高选择性极窄带滤波器的研究,滤波器的本质工作是选择有用的信号来过滤干扰信号,而对于无线系统来说,低插件滤波器非常有用,传统的射频微波平面材料设计这种滤波器将面临高Q值的问题。目前SAW(由IDT由压电材料组成,IDT将电信号转换为机械波(声波),再将机械波(声波)转换为电信号)滤波器,BAW滤波器(主要用于2.5GHz以上),小型3D堆叠腔滤波器是较好的研究点;

三是新材料、新工艺可集成在微系统中的小型滤波器研究中,如LTCC滤波器、介质滤波器、片上集成滤波器(IPD,CMOS,GaAs,SiGe BiCMOS,GaN等),基于液晶聚合物的小型射频滤波器等。

3.特定系统对滤波器的要求

也许一线研发的工程师会有深刻的理解,即当系统突然出现不必要的镜像干扰或其他未知的外部杂波时,工程师要么在原地旋转,要么像雪一样头发,怀疑银河系已经落了九天。这时,我突然发现滤波器还是挺香的。虽然它可能无法治愈所有疾病,但它基本上可以过滤掉许多不想要的信号。然而,在这个时候,系统通常不会给额外的滤波器太多的空间,许多奇怪的尺寸会出来。此时,我们的工程师需要出现粉末和墨水。根据各种异形尺寸要求和各种指标要求,我们可以通过骚操作获得不同的传输极点和零点,获得完美的滤波曲线,然后事情发生后,我刷了刷衣服,隐藏着我的身体和名字”。

综上所述,笔者认为在现代无线电子系统(尤其是20年)GHz低成本、高性能、小型化的滤波器将永远不会过时。本文也将基于2 μm GaAs HBT解释片上滤波器芯片的设计过程、设计原理和工程实现方法。

基本概念

滤波器定义:

顾名思义,滤波器是一种滤波器,主要用于选择有用信号和滤波器。

滤波器分类:

滤波器的分类标准很多,主要是基于用户关注的点。作者简要总结了以下分类,仅供参考:

根据传输函数:切比雪夫型;椭圆函数型;巴特沃斯型;准椭圆函数型等。

根据滤波功能:低通滤波器;带通滤波器;带阻滤波器;高通滤波器。

根据实现结构:发夹型;阶跃阻抗型;开口环型;二维码型;糖葫芦型等。

根据制造材料:介质滤波器;腔体滤波器、声表滤波器、体表滤波器等。

(题外话:据笔者观察,目前IEEE第三类滤波器包含在上面SCI大多数四个区域都可以在第一类修正相关理论后发表综合滤波器文章SCI1/2区。工业界大多集中在第四类滤波器的研究上,主要希望通过最简单的结构获得低成本、高可靠的滤波器,以满足系统要求)

滤波器的主要指标:

工作频率(f): 主要是指用户需要处理的信号的工作频率,如带过滤器的带,带过滤器的带是工作频率。

工作带宽(BW):如果没有特别声明,一般指3dB工作带宽,即与极值点(高低通滤波器为截止频率点)相比,所需选择的信号范围下降3dB工作频段的宽度。

插入损耗(IL):一般指信号的范围损失值(即二端口滤波器的输出波与输入波的比值取对数)。

电压驻波比(VSWR):一般用于衡量滤波器输入输出端口的回波量.5以下就够了,意思是只有4%左右的能量反射到输入口,96%已经发射出来了,而且和S11/S22具有与散射参数相同的功能(例如:端口1VSWR=(1 S11)/(1-S11),换成数值计算需要注意的是VSWR和S11的单位是不一致的,前者为功率表示,后者电压表示,因此后者换算成数值时需要把20除到等式另一侧,即相对VSWR开根号开根号)。

带外抑制度: 带外抑制是指带外信号的抑制程度,有时用矩形系数表示。系统设计更注重这些指标。在后续设计中,我们还将重点介绍相关的传输零引入技术,以实现带外信号的抑制。

滤波器设计理论

推荐参考微波基础和滤波器理论学习:

——Pozar微波工程;

——土井淳电磁场基本原理66课;

——Jia-Sheng Hong的《Microstripp Filter For RF/Microwave Aplplication》;

——Protap Pramanick的《Modern RF and Microwave Filter Design》;

以带通滤波器设计理论为例,设计所需滤波曲线主要有两种实用的底层数学逻辑:

从集中参数低通原型出发,通过频率变换获得集中参数电路模型,然后用不同的结构设计滤波器。这种方法对模拟工具匮乏的年代工程师非常有用。对于集总滤波器,相应的实际滤波器可以根据变化获得的电感电容值直接实现;大多数微带滤波器也需要根据kurda将电感电容值转换为实际电长和特性阻抗值,最终获得符合要求的分布式滤波器的实际尺寸。

从耦合矩阵开始,根据所需的耦合系数设计带滤波器。随着电磁仿真软件的发展,工程师可以轻松提取各种特性阻抗、电长、谐振器谐振频率和谐振器之间的耦合系数。因此,当设计师获得发布的设计任务时,只需要更多的指标来整合滤波器的耦合矩阵,并获得耦合系数(合理值),就可以很容易地设计出满足要求的耦合系数。本文运用耦合滤波器的经典理论抛砖引玉,欢迎大家讨论:

耦合型滤波器的低通原型电路

对于上图中的耦合滤波网,假设没有传输损耗,上述散射参数矩阵可以得到以下公式:

其中,n是谐振器的数量。E、P和F是和F被认为是复变量,ω0是一化频率。

此时滤波器的传输系数:

其中PN(S)是以s为变量的m阶多项式(m使传输系数为零的频率点被称作滤波器的传输零点。ε是在ω=±1归一化的常数:

其中RL表示滤波器的回波损耗(Retrun Loss)。上文提到的按照响应函数对滤波器分类下表给出了常见的传输函数S21的分类:

表1 常见滤波器传输函数及滤波器分类

同理,由上面的散射矩阵可得反射系数为:

其中FN是n阶首项为1的多项式,EN是归一化Hurwitz多项式。并满足下面的谱方程:

使滤波器反射系数为零的复频率点被称作反射零点或传输极点。

看完这些理论大家先不要慌,不要觉得复杂。既然数学本身不是为了让事情更加复杂,而是为了让事情变得更加简明,同时我们很多时候设计滤波器就是在调试滤波器的极点和零点所在位置,那么对于传输零点与极点的设计我们用什么数学方法更加简单呢?

有!笔者认为答案是:耦合矩阵!!!(后期我们的芯片滤波器也是先通过软件综合出耦合矩阵,再变换到集中元件,最后做EM仿真得到最终版图)

由于篇幅原因以及前期有RFASK相关专栏作者分享过耦合矩阵的Matlab实现代码(基本上大家可以从代码中看到其数学推导过程),因此对于由低通原型到传输函数,再到导纳矩阵,再到耦合矩阵,再由相似变换简化耦合矩阵这个相对复杂的数学过程本文就不再讨论了,本文主要抛出常见的实现带通滤波器耦合矩阵的“CT(Cascaded Triplet)”与“CQ(Cascaded Quadruplet)”拓扑结构,来简单讨论其底层的数学逻辑。

CT,CQ拓扑利用信号传输的相位关系,可以独立地产生一个或两个传输零点,而与其它谐振器无关,这样有利于设计师们独立地设计调试各个部件。下图展示两款带通滤波器的CT拓扑结构的单元电路,其中1,2,3分别表示谐振器1,谐振器2与谐振器3,谐振器之间的度数表示不同的耦合方式:

现在大家跟着我一起来做一个简单的数学题,看看可不可以把这两个CT结构单元电路的传输零点的位置找出来:

先让大家玩个小游戏,找找看上图这两个CT结构有什么不同???

答案揭晓:谐振器1与谐振器3的耦合方式不同,也就是CT拓扑1的源负之间(1,3谐振器之间)的耦合采用的电耦合,CT拓扑2采用的磁耦合。

对于CT拓扑1的结构,假定信号从谐振器1出发,经过两条路径(a与b)到达谐振器3,同时假设此时的信号在相对于中心频率的低频端(咋们自信点,极限一点,就让此时信号经过谐振器的相位与中心频率相位差为+90°),那么,请问此时信号能不能传输到谐振3???

如上表所示,由于低频端的信号经过a,b两路后相位差为180°,即此时低频端的信号(相对中心频率相位差为+90°)不能传输过去,因此在低频端(与中心频率相位差+90°处)产生了一个传输零点,如下图所示:

同样的道理,CT拓扑2的高频端信号(与中心频率相差-90°),由1→A→3与1→B→3两条路径也不能由谐振器1传输到谐振器3,因此CT拓扑2的耦合矩阵得到的滤波器能够在高频端获得一个传输零点,如下图所示:

对于引入了两个传输零点的CQ结构,也可以按照此类方法分析。由于CQ结构的组合较多,本文先给出如下图所示的一个CQ拓扑结构的传输相位关系的数学推导(其余的CQ拓扑的数学推导,大家可以自行下来算算哦):

针对上图所示简化版的CQ模型中有如下结论:想要利用CQ拓扑在中心频段上下两个边带分别获得一个零点,满足“谐振器同步调谐,耦合边两同两异”即可。这里读者朋友可能就要问了,老师你发明的啥子词语哦,啥叫“谐振器同步调谐,耦合边两同两异”呢??OKay,“谐振器同步调谐”主要就是保证当信号进入输入端时,瞬间传输到输出端,假定了(这是理论模型,只是假定哦,求不杠)信号在所有谐振器中几乎没有什么损耗且相位一样,而“耦合边两同两异”主要就是保证两路信号在高/低频时相位保持180°的相位差,笔者这里用下图来解释下:

如上图,本文的CQ模型中所谓的“耦合边两同两异”即耦合边Mm-1,m+2与Mm,m+1的耦合方式不同,而耦合边Mm-1,m与耦合边Mm+1,m+2的耦合方式相同。

好啦,其实滤波器的理论心法还有很多方向去写,由于篇幅原因,今天就歇了,如果后面大家感兴趣的话,咋们再来聊聊。下面即将进入芯片滤波器设计的主题。

芯片滤波器的设计

对于芯片滤波器的设计,是不是主要利用低通原型,查找真值表,然后频率变换得到想要的集中参数,最后来实现想要的频率响应呢?其实对也不对,因为芯片滤波器会有比较多的应用场景,不同的场景所采用的方法还是有一点点区别,本文主要目的是让大家了解芯片滤波器的设计流程,采用一个实际例子给大家展示具体的芯片滤波器过程(本次设计采用ADS2022仿真工具)。

本设计实例主要按照如下内容展开: ①设计约束,讲解芯片设计前期考虑;②滤波器原型综合,利用耦合矩阵得到相应的原型响应曲线;③滤波器原理图仿真,根据耦合矩阵推导出对应的电感、电容值,并适当调试得到前仿结果;④滤波器电磁(EM)仿真,考虑布局布线对滤波器的影响,仿真得到最终值;⑤版图绘制与DRC。

——设计约束:

(1)工艺约束,由于本次准备设计的射频滤波器拟采用无源结构来实现,因此工艺节点对设计本身的约束较小,但之所以没有采用常用的IPD工艺,是因为便于与某射频前端系统中的其他模块集成,因此拟采用某2 μm GaAs HBT工艺;

(2)指标约束,本次设计主要是举例为主,设计了一款Sub-6GHz的滤波器,具体的指标不做过多展开,后续在带通滤波器的基础上我会加一个传输零点的控制的M外推型电路,便是基于提高带外抑制度的考虑。读者需要注意的是,在实际工程中的指标约束可以是系统其他模块电路根据相应需求提出的,也可以是系统应用背景要求的,滤波器设计师很多时候往往是人在江湖,身不由己,只有玩命撸指标咯,如果实在怼不出来再去和PM argue吧。

(3)尺寸约束,在片上实现滤波器结构,自然是尽可能地小(芯片每平米的价格可比北上广的房价贵哦),本设计实例没有采用上文提到的CQ结构来实现一对传输零点的引入,而是采用只有两个谐振器的源负耦合,来实现有一对传输零点的带通滤波器,正是基于能少用谐振器就是少用的原则来做的。

——滤波器原型综合:

如上设计约束中提到的,本次采用如下图所示耦合拓扑结构,在输入端(S)与输出端(L)之间插入两个谐振器(1,2),谐振器之间构建两路不同的耦合,一路(1→a→2),一路(1→b→2),根据上文中提到的基本分析方法可知,当信号偏离中心频率的相位差+90°与-90°时,S到L的信号相位之和都差180°,因此可以实现一对传输零点。

此时根据设计指标,利用耦合矩阵综合软件(可以是之前RFASK的博主分享的也可以自己在Matlab里面编写)建立上图拓扑,然后得到耦合矩阵以及原型响应曲线如下:

——滤波器原理图设置以及仿真:

根据综合得到的耦合矩阵,然后计算得到谐振器以及耦合之路的电感电容值,具体的推导不在赘述,下面给出本文中的理论方法:

此时

其中Y0为1/50Ω-1,Ci为自定义的归一化电容值。然后在ADS2022中搭建原理图仿真得到如下结果:

上图基本实现了一对传输零点的引入,下面再在ADS Momentum中搭建电磁仿真模型。

——滤波器电磁(EM)仿真:

(1) 感值、容值及其Q值的提取。在进行电磁仿真时,可以在控制面板中调出厂家提供的电感,电容进行整版仿真,不过一般实际工程中会先对电感,电容值进行提取,以获得准确的电感/容值和其Q值。如下图所示,我们对常见的电感进行电磁仿真,提取其感值和Q值,对比方形螺旋电感(Square spiral inductor,SSI)、八边形螺旋电感(Octagonal spiral inductor,QSI)、圆形螺旋电感(Circular spiral inductor,SSI)分析发现,圆形螺旋的电感Q值相对较高,后续在厂家版图规则允许的前提下我们选用Q值较高的电感。

对于电容的选择,读者可以根据厂家的Guide文件查看其分类,一般在射频微波频段用厂家提供的面积小,Q值相对较高的MIM电容较多,如果频率到了毫米波可能会自行设计电容(如平板电容,交趾电容等),本文就不对电容做特殊分析了。

(2)整版仿真。根据提取到的电感电容模型值,在ADS Momentum中搭建如下图所示版图,然后再在EM ->Simulation settings里面设置好仿真条件。需要注意的是求解器的选择,每个导波波长内的网格划分cells数以及边沿网格的选择很多时候会影响到设计的准确度。设置好后仿真得到如下结果:

(3)对仿真结果进行分析,发现问题,解决问题,改进滤波器的性能。

发现问题:针对上述整版电磁仿真结果发现在18GHz处产生了一个寄生通带,且7GHz~18GHz的带外抑制度较差;

原因分析:分析其原因主要是谐振器的寄生参数引入的寄生谐振以及在引入交叉耦合(上文中提到的1→b→2路径)时外加的传输线引入了寄生谐振频率。

解决方案:其实在传统的PCB滤波器也会有寄生通带,微带滤波器的处理方法较多,比如谐振器之间采用不同形状(每个谐振器的寄生通带不一样,级联后可以整体消除寄生通带)、谐振器采用如SIR(阶跃阻抗谐振器)等具有通带抑制的结构,但是在芯片内部相对集总参数的谐振器处理相对较难,因此本文采用了一种零点引入技术,在10 GHz引入传输零点,加大对寄生通带的抑制。具体而言,采用引入传输零点的Pi型电路,如下图所示

其中,fTZ = 10 GHz, f0 = 3 GHz, ZF = 50 Ω and ZP = 82 Ω(Zp是对上文版图的输出端口阻抗提取得到的值)那么可以推导出对芯片进行重新绘制电磁仿真模型,得到如下仿真结果

——版图绘制与DRC:

与硅基射频电路的版图相比,III-V族化合物电路设计完后的版图一般不需要做金属密度填充,对晶体管外的衬底的处理相对较少。因此本文的版图设计要点主要有:对外Pad应该满足封装要求,如果是内部集成到系统应该满足其他模块的设计要求;金属走线,器件放置等应该满足厂家的DRC( design rule check);最终版图导出后,如果要与系统其他模块集成,尽量将其打散(先选中版图,然后按照下图操作),以免将模块给冲掉。

——END——

后记:滤波器的理论要求相对较高,本文涉及不及万分之一,仅仅展示了一种相对容易的数学方法结合仿真软件来实现芯片滤波器的设计,前前后后码字到眼花,仓促之间难免有纰漏,希望各位兄弟姐妹能积极讨论修正哦

另外兄弟姐妹们,您的点赞分享或打赏将是我继续写下去的无限动力哦~

《射频微波芯片设计》系列文章将持续更新,安排如下图所示:

作者:RFIC_抛砖

来源:https://www.rfask.net/article-614.html

关于RFASK射频问问

射频问问 (RFASK.NET) 是在"微波射频网 (MWRF.NET)”系列原创技术专栏基础上升级打造的技术问答学习平台,主要围绕射频芯片、微波电路、天线、雷达、卫星等相关技术领域,致力于为无线通信、微波射频、天线、雷达等行业的工程师,提供优质、原创的技术问答、专栏文章、射频课程等学习内容。更多请访问:www.rfask.net