数字电路基础与Quartus-II入门

时间:2023-06-08 08:07:00

数字电路基础与Quartus-II入门

- 一、D触发器

-

- 1.简介

- 2.结构

- 3.工作原理

- 4.特征

- 5.脉冲特性

- 二、在 Quartus-II 用门电路设计D触发器并进行模拟,验证时序波形

-

- 1.在Quartus中新建工程

- 2.创建原理图文件

- 3.编译原理图文件

- 4.创建VWF文

- 5.波形仿真

- 三、在 Quartus-II D触发器电路直接调用模拟,时序波形验证

-

- 1.新建工程

- 2.创建原理图

- 3.编译原理图

- 4.创建VWF文件

- 5.波形仿真

- 四、总结

一、D触发器

1.简介

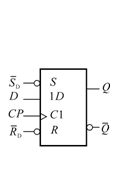

D触发器是一种具有记忆功能和两种稳定状态的信息存储设备,是构成各种时间电路的最基本的逻辑单元,也是数字逻辑电路中的重要单元电路。因此,D触发器广泛应用于数字系统和计算机。触发器有两种稳定状态,即"0"和"1",在一定的外部信号作用下,可以从稳定状态转向另一个稳定状态。D触发器由集成触发器和门电路组成。有两种触发方法:电平触发和边缘触发CP(时钟脉冲)=1时即可触发,后者多在CP前沿(正跳0→1)触发。D触发器的次态取决于触发前D端的状态=D。因此,它具有置0和置1两种功能。对于边缘D触发器,因为在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D数据状态的变化不会影响触发器的输出状态。D触发器广泛应用于数字信号寄存、移位寄存、分频和波形发生器等。

2.结构

D触发器(data flip-flop或delay flip-flop)由四个非门组成,其中G1和G2构成基本RS触发器。电平触发的主从触发器工作时,必须在正跳前添加输入信号。如果在CP如果在高电平输入端出现干扰信号,触发器的状态可能会出错。边缘触发器允许CP将输入信号添加到触发沿的前一刻。这样,输入端受干扰的时间大大缩短,受干扰的可能性降低。边缘D触发器又称维护-阻塞边缘D触发器。两个D触发器可以串联边缘D触发器,但第一个D触发器CP非门反向需要使用。

3.工作原理

SD和RD接至基本RS低电平有效的触发器输入端分别为预置和清洗端。当SD=1且RD=0时(SD的非为0,RD非1,即由于低电平有效,在两个控制端口分别从外部输入的电平值),无论输入端D处于何种状态,都会使Q=0,Q非=1.触发器0;当SD=0且RD=1(SD的非为1,RD当,Q=1,Q非=触发器1,SD和RD也叫直接置1和置0端。在不影响电路工作的情况下,我们设置了高电平。

工作流程如下:

1)CP=0时,与非门G3和G封锁,其输出Q3=Q4=1.触发器状态不变。同时,因为Q3至Q5和Q4至Q6反馈信号打开这两扇门,因此可以接收输入信号D,Q5=D,Q6=Q5非=D非。

2)当CP触发器从0变1翻转。G3和G打开它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5非=D非,Q4=Q6非=D。由基本RS可以看出触发器的逻辑功能,Q=Q3非=D。

3)触发器翻转后,CP=输入信号在1点被封锁。这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,也就是说,必须有0,如果Q3为0,则经G3输出至G将输入反馈线G5封锁,即D通向基本封锁RS触发器路径;反馈线使触发器保持在1状态,防止触发器变成0状态,因此反馈线称为1维持线和0阻塞线。Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁了。Q4输出端至G6反馈线使触发器保持在0状态,称为设置0维持线;Q4输出至G输入反馈线起到阻止触发器置1的作用,称为置1阻塞线。因此,触发器通常被称为维护-阻塞触发器。

总之,触发器在CP正跳边缘接收输入信号,正跳边缘触发翻转,正跳边缘后输入封锁,正跳边缘后三步完成,称为边缘触发器。与主触发器相比,同一工艺的边缘触发器具有更强的抗干扰性和更高的工作速度。 /span>。由基本RS可以看出触发器的逻辑功能,Q=Q3非=D。

4.特征

5.脉冲特性

1)建立时间

由于CP信号加到门口G3和G四上,所以在CP上升沿前门G5和G输出端状态必须稳定建立。输入信号到达D端后,通过一级门电路传输延迟时间G建立5的输出状态,G6的输出状态需要经过两级门电路的传输延迟时间才能建立,因此D端的输入信号必须先于CP上升沿到达,建立时间应满足:tset≥2tpd。

2)保持时间

为实现边缘触发,应保证CP=1期间门G5的输出状态不变,不受D端状态变化的影响。为此,在D=在0的情况下,当CP上升沿到达后,您必须等待门G3输出低电平返回门G5输入端后,D允许改变端部的低电平。因此,低电平信号输入的维护时间是tHL≥tpd。在D=因为CP上升沿到达后G4的输出将G3.封锁,因此不需要输入信号保持不变,因此高电平信号的输入保持时间tHH=0。

3)延迟传输时间

从CP上升沿到达时开始计算,输出从高电平延迟到低电平tPHL从低电平到高电平的传输延迟时间tPLH分别是:tPHL=3tpdt PLH=2tpd。

4)最高时钟频率

为保证由门G1~G4组成的同步RS触发器可以可靠地翻转,CP高电平的持续时间应大于 tPHL,因此,时钟信号的宽度的宽度tWH应大于tPHL。而下一个CP上升沿到达之前确保门G5和G稳定建立新的输出电平,CP低电平的持续时间不得小于门G4传输延迟时间和tset即时钟信号低电平的宽度之和tWL≥tset tpd。

在实际的集成触发器中,每扇门的传输时间不同,简化了不同的形式,因此上述讨论的结果只是一些定性的物理概念。其真实参数由实验确定。

在考虑建立时间时,应考虑时钟树向后倾斜,在考虑建立时间时,应考虑时钟树向前倾斜。最大延迟用于检查建立时间,最小延迟用于检查建立时间。

时间限制与时钟周期有关。当系统在高频时钟下不能工作时,降低时钟频率可以使系统完成工作。维护时间是一个与时钟周期无关的参数。如果设计不合理,布线工具不能布置高质量的时钟树,无论如何调整时钟频率都不能满足要求,只有设计系统才能正常工作,导致设计效率大大降低。因此,合理设计系统的顺序是提高设计质量的关键。时钟树的偏差在可编程设备中几乎可以忽略不计,所以保持时间通常是满足的。

二、在 Quartus-II 用门电路设计D触发器并进行模拟,验证时序波形

1.在Quartus中新建工程

2.创建原理图文件

点击【插头图标】弹出工具窗口,搜索元件,然后在图纸上摆放:

4 个 nand2 与非门;

1 个 not 非门。

添加两个输入管脚和两个输出管脚,双击 Pin Name 即可修改管脚名。

完整图如下

保存电路图

3.编译原理图文件

点击编译

查看硬件电路图:点击【Tools】→【Netlist Viewers】→【RTL Viewer】。

4.创建VWF文

编辑输入CLK,产生时钟信号

保存文件

时序仿真(一个时钟的延迟)

四、总结

相较于第二部分,来说,使用现有的D触发器会更加方便,绘图少,但是对于D触发器的内部结构来说不太清楚,最后仿真出来的结果也是一样的。

参考链接

https://blog.csdn.net/ssj925319/article/details/115355019?spm=1001.2014.3001.5502

https://blog.csdn.net/qq_43279579/article/details/115286467