【题目精刷】2022大疆-数字芯片-B

时间:2023-01-15 22:00:00

为了在做题题的过程中学习所需的知识,详细说明了每个问题的知识参考或知识细节。后续复习。欢迎批评和纠正文章中的答案。

题目评价

- 难易程度:★★★☆☆

- 知识覆盖:★★★☆☆

- 超纲范围:★★☆☆☆

- 值得一刷:★★★★☆

值得一刷。

文章目录

-

-

-

- 1、下列关于mbist正确的测试描述之一是:

- 2.芯片中信号串扰描述的以下错误之一是:

- 3.关于异步复位,以下说法是正确的:

- 4、1个16Kx8位存储器的地址线和数据线总和为()

- 5.以下关于多bit数据跨时钟域的处理思路是错误的

- 下载编程文件/调试物理FPGA设备的通信技术名称是什么?

- 7.嵌入式设备包括linux内核,bootrom,bootloader,文件系统镜像system.img,嵌入式设备启动时的启动加载顺序是什么?

- 8、预设clk为周期为10ns时钟可以在以下选项中正确使用clk延时8ns的clk_dly信号是:

- 9、32bit位宽的异步fifo,写时钟1000M,读时钟速率800M,数据包大小为4KB,当间隔足够大时,fifo最小深度为()

- 10、下列属于DFT质量测量指标包括:

- 11、下列关于OCC(on chip clock controller)正确的行为描述是:

- 12.芯片流片前的以下检查包括:

- 13.标准单元动态功耗与以下因素有关?

- 14、关于16点FFT正确描述是()

- 15.以下哪些活动可以通过形式验证

- 根据约束关系set_clock_groups -asynchronous -group {CLK1} -group {CLK2 CLK3}下图中的时序检查路径是什么?

- 17、随着IC随着电路设计技术的进步,漏电功耗的比例越来越大。不考虑温漂的影响,以下技术可以用来降低漏电功耗?

- 18、在SOC以下哪些选项属于验证应用?Emulator(仿真加速器)的特点

- 假设,在某SoC有一个环境UART在将控制器连接到主机并打开串口工具进行连接后,假设所有硬件电路故障都被排除在外,以下说法是正确的:

-

-

1、下列关于mbist正确的测试描述之一是:

- A、mbist测试实现无面积开支

- B、mbist测试频率和mem工作频率不一致

- C、mem repair能提高良率

- D、mbist测试对mem性能没有影响

存储器内建自测(memory built-in self-test,MBIST)

内建自测的基本思想:电路自己生成测试向量,而不是要求外部施加测试向量。它有独立的比较结构来决定得到的测试结果是否正确。

A: 因此,内建自测必须增加额外的电路。

B: mbist测试频率和mem只有工作频率一致,才能检查实际工作中的耦合故障。

C: mem repair:通过DFT检测出某些mem单元读写错误(芯片制造后出现随机问题、电路错误或性能无法达到),此时可以使用一些规则和算法mem中原本富余的逻辑来替换这部分单元。所以肯定是可以提高良率的。

D:没有找到具体的参考,测试只完成测试功能,对性能没有影响;但有些数据说MBIST有Mbist Repair功能,如果修复故障单元,性能必须提高。

2.芯片中信号串扰描述的以下错误之一是:

- A、串扰会导致信号延迟和毛刺

- B、增强侵犯网络单元的驱动能力,减少串扰影响

- C、将缓冲器插入受害网络可以减少串扰

- D、增加导线间距可以减少串扰

芯片上的串扰(Crosstalk)串扰是由互连线之间的寄生耦合引起的噪声,反映了物理世界的非理想特征。随着芯片特征尺寸的细化,互连线的物理尺寸和间距变小,导致互连线之间的耦合效应增加,串扰产生和增强。

侵害网络(aggressor net或attacker):网络产生串扰信号源。

受害网络(victom net):接收串扰网络。

串扰会导致信号延迟和毛刺,从而影响芯片的顺序性能和正常功能。

- 侵权网络的上升沿变化在受害网络中产生相应的串扰,导致信号非单调转换,产生毛刺(glitch)。

- 串扰使信号转换变慢或变快称为串扰延迟。当受害者被拉高时,一个拉高串扰被侵犯,使转换变快,导致hold违规。相反会导致setup违例。

串扰预防:

- 保护受害者网络。增加间隔,使用屏蔽和使用金属保留层。适用时钟和其他高风扇出网,但会占用额外的布线空间和资源。

- 增强受害者网络的免疫力。尽量在串扰噪声干扰破坏性强的异步网络上使用高驱动单元。

串扰修复:

- 增强驱动单元的能力。增加受害者网络上驱动器的单元驱动能力。如果驱动能力强,串扰的影响会更小。

- 将缓冲器插入受害者网络。可解决电容串扰噪声脉冲、过压、电压过低等问题。由功能故障、延迟和竞争条件引起。

- 插入延迟单元。修复最小延迟干扰(hold违例)。

- 采用网络排斥法。合理利用互斥网络。

- 调整布线。确定哪条干扰路径包含在一组必须听网络排斥修复的路径中。

B: 相反,受害网络的单元驱动能力需要增强。

3.关于异步复位,以下说法是正确的:

- A、奇存器的时钟状态是否否可以复位没有影响

- B、奇存器的时钟状态是否能解复位并不影响

- C、复位信号上是否有毛刺?

- D、异步复位信号不需要同步到相应的时钟域

A、B: 恢复时间和移除时间需要满足:

- 寄存器的恢复时间:复位/位置信号到达时钟翻转到达时间。也称为复位/位置信号的建立时间。i>

- 寄存器的移除时间:时钟边沿之后复位/置位信号必须保持有效的时间。也被称为复位/置位信号的保持时间。

C: 异步复位对毛刺敏感。

4、1个16Kx8位的存储器,其地址线和数据线总和是()

- A、48

- B、46

- C、17

- D、22

16K深度,地址线为 (4+10) = 14位。

数据线8位。

5、下列关于多bit数据跨时钟域的处理思路,错误的有()

- A、发送方给出数据,发送方给出握手请求,接收方收到后回复,发送方撤销数据。

- B、发送方给出数据,接收方用本地时钟同步两拍再使用;

- C、发送方把数据写到异步fifo,接收方从异步fifo里读出;

- D、对于连续变化的信号,发送方转为格雷码发送,接收方收到后再转为二进制。

A: 方案是握手协议,思路是等多bit数据稳定,然后通过但bit握手信号对稳定后的数据进行采样,可以减小亚稳态概率。

B: 多bit不可以

C: FIFO

D: 格雷码

6、用于下载编程文件/调试物理FPGA器件的通信技术名称是什么?()

- A、HDMI

- B、USV

- C、JTAG

- D、JPEG

???

7、某嵌入式设备包含linux内核,bootrom,bootloader,文件系统镜像system.img,则它们在嵌入式设备开机时的启动加载顺序为?

- A、linux -> bootrom -> bootloader -> system.img

- B、bootrom -> bootloader -> linux -> system.img

- C、bootloader -> system.img -> linux -> bootrom

- D、linux -> system.img-> bootrom -> bootloader

嵌入式Linux OS启动流程:

- 硬件上电

- 一级启动:bootROM

将二级程序引导程序SPL(Secondary Program Loader)加载到RAM运行。 - 二级启动:SPL+bootloader

- Linux内核

- 不同的OS

8、预设clk为周期为10ns的时钟,以下选项中能正确将clk延时8ns的clk_dly信号是:

- A、assign #8ns clk_dly = clk;

- B、assign #8ns clk_dly <= clk;

- C、always@(clk) begin clk_dly = #8ns clk; end

- D、always@(clk) begin clk_dly <= #8ns clk; end

Verilog 延时模型

实际延迟值单位是时间单元决定,不带单位。

A: 连续赋值过程定义延迟。右侧更新数据后等待期间如果发生了数据改变,则刷新等待时间,即只有持续延时时间的信号会被延时赋值给左侧。周期为5ns,所以这句的结果是clk_dly一直保持。

B:没有这种用法

C: 阻塞过程性延迟赋值,与A类似。

D: 非阻塞过程性延迟赋值。

9、32bit位宽的异步fifo,写时钟1000M,读时钟速率800M,在数据包大小为4KB,包间隔足够大时,fifo的最小深度为()

- A、158

- B、205

- C、638

- D、820

包间隔足够大,只需要考虑一包的缓存。

FIFO数据位宽32bit。4KB对应1k个数据。

写时钟1000MHz,写1K个数据需要的时间: 1 1 M \frac{1}{1M} 1M1

这个时间读了: 800 M ∗ 1 1 M = 800 800M*\frac{1}{1M}=800 800M∗1M1=800个数据,读的过程FIFO越来越满,直到之后FIFO中还剩200个数据。

所以FIFO深度大于200个就行。

10、下列属于DFT质量的衡量指标有:

- A、测试覆盖率

- B、测试电路面积开销

- C、测试时间

- D、故障模型

衡量指标。

11、下列关于OCC(on chip clock controller)行为描述正确的是:

- A、用于控制高频和低频测试时钟的切换

- B、用于控制产生指定数目的shift时钟

- C、用于控制产生指定数目的capture时钟

- D、切换过程可能产生毛刺

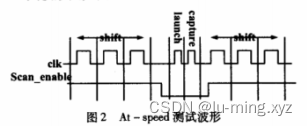

参考:《如何用OCC电路实现at-speed测试_李冬》OCC(On-Chip-Clock)含义及功能和结构

At-speed 测试:面向电路内部引入延迟的故障,检测电路工作在一定频率下,电平翻转无法在一定时间内完成的故障。

一般芯片内部由CRG(Clock Reset Generation)模块提供系统工作所需的各种时钟,然后提供给各模块使用。为了支持At-speed测试,需要在CRG和模块之间加入OOC电路,OOC电路支持的功能:

- 正常功能模式下输出系统时钟

- stuck-at模式下输出测试机慢速时钟

- at-speed模式下输出测试所需的时钟。

OOC的结构示意图:

所以A、B、C是对的。

D没有找到资料,作为在固定工作模式切换时钟的模块,个人认为MUX结构切换过程可能产生毛刺,但是并不影响,在完成切换后才进行对应测试的。

12、下列属于芯片流片前的检查有:

- A、设计规则检查

- B、天线效应检查

- C、电路与版图一致性检查

- D、形式验证

不会做。

IC 流片前的Check List:

- 布局检查

- 走线检查

- 驱动/负载检查

- IO 检查

- 设计规则检查

13、下列哪些因素与标准单元动态功耗有关?

- A、工作频率

- B、工作电压

- C、亚阈值泄漏电流

- D、输出负载

CMOS 电路功耗类型:

- 动态功耗:负载电容充放电引起的功耗。

- 静态功耗:漏电流引起的功耗。

P = 1 2 ⋅ C ⋅ V D D 2 ⋅ f ⋅ N S W ⏟ 翻 转 功 耗 + Q S C ⋅ V D D ⋅ f ⋅ N S W ⏟ 短 路 功 耗 ⏞ 动 态 功 耗 + I l e a k ⋅ V D D ⏟ 漏 电 流 功 耗 ⏞ 静 态 功 耗 P=\overbrace{\underbrace{ \frac{1}{2}·C·V^2_{DD}·f·N_{SW}}_{翻转功耗} + \underbrace{Q_{SC}·V_{DD}·f·N_{SW}}_{短路功耗}}^{动态功耗} + \overbrace{\underbrace{I_{leak}·V_{DD}}_{漏电流功耗}}^{静态功耗} P=翻转功耗 21⋅C⋅VDD2⋅f⋅NSW+短路功耗 QSC⋅VDD⋅f⋅NSW 动态功耗+漏电流功耗 Ileak⋅VDD 静态功耗

- C C C:结电容。

- N S W N_{SW} NSW:单周期内翻转晶体管数目。

- f f f:系统工作时钟频率。

- V D D V_{DD} VDD:供电电压。

- Q S C Q_{SC} QSC:翻转过程中的短路电量。

- I l e a k I_{leak} Ileak:漏电流。

C: 静态功耗

D: 输出负载体现在 C C C:结电容。

14、关于16点FFT描述正确的是()

- A、共有4级分解;

- B、每级有8个蝶形算法;

- C、每个蝶形算法需要1次复数乘法;

- D、每个蝶形算法需要1次复数加法;

库利-图基算法(DIT-FFT)特点:

- 共 l o g 2 N log_2^N log2N级运算,16点FFT即4级运算。

- 每一级有 N / 2 N/2 N/2个蝶形运算

- 每个蝶形需要一次复数乘法和两次复数加法。

{ X M [ i ] = X m − 1 [ i ] + W N r X m − 1 [ j ] X M [ j ] = X m − 1 [ i ] − W N r X m − 1 [ j ] \left\{ \begin{aligned} X_M[i]=X_{m-1}[i]+W_N^rX_{m-1}[j] \\ X_M[j]=X_{m-1}[i]-W_N^rX_{m-1}[j] \end{aligned} \right. { XM[i]=Xm−1[i]+WNrXm−1[j]XM[j]=Xm−1[i]−WNrXm−1[j]

15、以下哪些活动可以通过形式验证保证

- A、RTL和RTL的一致性

- B、RTL的功能完整性

- C、RTL和综合网表的一致性

- D、两张不同网表的一致性

形式验证的目标

- RTL与RTL:确认新的RTL与原来RTL在功能上是否一致。

- 门级网表与RTL:确定DC综合的逻辑是正确的。

- 两个门级网表之间:确认版图输入信息与版图输出信息。