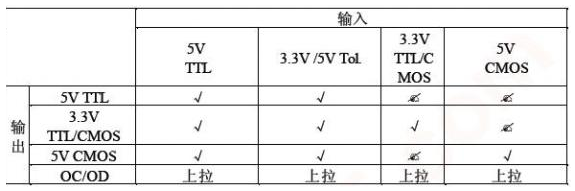

TTL与CMOS电路小结

时间:2023-01-11 08:00:00

目录

- 简介

-

- 噪声容限

- TTL电路

- CMOS电路

- CMOS集成电路的性能和特点

-

- 功耗低

- 工作电压范围宽

- 逻辑摆幅大

- 抗干扰能力强

- 输入阻抗高

- 良好的温度稳定性

- 扇出能力强

- 抗辐射能力强

- 可控性好

- 接口方便

- 建议使用设备

- OC/OD门

- 参考文献

简介

TTL—Transistor-Transistor Logic 三极管-三极管逻辑

MOS—Metal-Oxide Semiconductor 金属氧化物半导体晶体管

CMOS—Complementary Metal-Oxide Semiconductor金属氧化物半导体晶体管

| 类型 | 输入 | 输出 |

|---|---|---|

| TTL | L: <1.2V ; H:>2.0V | L: <0.8V ; H:>2.4V |

| CMOS | L<0.1* Vcc H>0.9 * Vcc | <0.3 * Vcc H:>0.7 * Vcc |

噪声容限

TTL设备输出低电平小于0.8V,高电平大于2.4V。输入,低于1.2V它被认为是0,高于2.所以TTL低电平输入的噪声容量仅为(0.8-0)/2=0.4V,高电平噪声容量为(5-2.4)/2=1.3V。

假设CMOS电源采用12V,则输入低于3.6V噪声容量为1.8V,高于3.5V噪声容量为1.8V。比TTL噪声容限较高。

TTL电路

TTL电路以双极晶体管(三极管)为开关元件,也称为双极集成电路。双极数字集成电路是利用两种不同极性的载流子进行电传导的装置。

它具有速度高(开关速度快)、驱动能力强等优点,但功耗大,集成度相对较低。

根据不同的应用领域,分为54系列和74系列,前者是军用产品,一般工业设备和消费电子产品多用于后者。

74系列数字集成电路是世界上常见的标准电路。其品种分为74(标准)和74六类S(肖特基),74LS××(低功耗肖特基),74AS××(先进肖特基),74ALS××74F××(高速),其逻辑功能完全相同。

CMOS电路

CMOS该电路由绝缘场效应晶体管组成,是一种单极晶体管集成电路,因为它只有一个载流子。

它的主要优点是输入阻抗高、功耗低、抗干扰能力强适用于大规模集成。特别是其主导产品CMOS集成电路具有静态功耗几乎为零、输出逻辑电平等特殊优点VDD或VSS,上升和下降时间在同一数量级,因此CMOS集成电路产品已成为集成电路的主流之一。

其品种包括4000系列CMOS74系列高速及高速公路CMOS电路。74系列高速CMOS电路分为三类:HC为CMOS工作电平;HCT为TTL工作电平(可与744相同)LS系列交换使用);HCU适用于无缓冲级CMOS电路。74系列高速CMOS电路的逻辑功能和引脚排列与相应的74LS该系列品种相同,工作速度当高,功耗大大降低。

74系列可以说是我们平时接触最多的芯片,74系列有很多种,我们平时使用最多的应该是以下几种:74LS,74HC,74HCT这三种

| 类型 | 输入电平 | 输出电平 |

|---|---|---|

| 74LS | TTL电平 | TTL电平 |

| 74HC | CMOS电平 | CMOS电平 |

| 74HCT | TTL电平 | CMOS电平 |

另外,随着推出BiCMOS集成电路集成了双极和MOS集成电路的优点,普通双极门电路的优点逐渐消失,一些曾经占据主导地位的TTL该系列产品正逐渐退出市场。CMOS门电路不断改进工艺,正朝着高速、低耗、大驱动能力、低电源电压的方向发展。BiCMOS集成电路的输入门电路采用CMOS工艺,其输出端采用双极推拉式输出方式CMOS具有双极优势,已成为集成门电路的新宠。

CMOS集成电路的性能和特点

功耗低

CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通另一个管截止的状态,电路静态功耗理论上为零。实际上,由于存在漏电流,CMOS电路仍有微量静态功耗。单门电路的典型功耗值仅为20mW,动态功耗(1MHz工作频率只有几个mW。

工作电压范围宽

CMOS集成电路供电简单,供电量小,基本不需要稳压。CC集成电路4000系列,可在3~18V正常工作在电压下。

逻辑摆幅大

CMOS逻辑高电平集成电路"1"、逻辑低电平"0"分别接近于电源高电位VDD电源低电位VSS。当VDD=15V,VSS=0V当输出逻辑摆幅接近15时V。因此,CMOS各种集成电路中集成电路的电压利用系数较高。

抗干扰能力强

CMOS集成电路电压噪声容量的典型值为电源电压的45%,保证值为电源电压的30%。

随着电源电压的增加,噪声容量电压的绝对值将成比例增加。VDD=15V的供电电压(当VSS=0V),电路将有7V左右噪声容限。

输入阻抗高

CMOS集成电路的输入端一般是由保护二极管和串联电阻组成的保护网络,略小于一般场效应管的输入电阻,但在正常工作电压范围内,直流输入电阻取决于二极管的泄漏电流,通常等效输入电阻高达103~1011?,因此CMOS集成电路几乎不消耗驱动电路的功率。

良好的温度稳定性

由于CMOS集成电路功耗低,内部热量少,CMOS电路结构和电气参数是对称的,当温度环境发生变化时,一些参数可以自动补偿CMOS集成电路的温度特性很好。一般陶瓷金属封装电路工作温度为-55 ~ 125℃;塑料封装的电路工作温度范围为-45 ~ 85℃。

扇出能力强

风扇输出能力由电路输出端驱动的输入端数表示。CMOS集成电路的输入阻抗很高,因此电路的输出能力受输入电容的限制,但当CMOS如果不考虑速度,集成电路通常可以驱动50个以上的输入端。

抗辐射能力强

CMOS集成电路中的基本装置是MOS晶体管是大多数载流子导电设备。各种射线和辐射对其导电性能的影响有限,特别适用于航天和验证设备的生产。

可控性好

CMOS集成电路输出波形的上下时间可以控制,其输出的上下时间的典型值是电路传输延迟时间的125%~140%。

接口方便

因为CMOS集成电路输入阻抗高,输出摆幅大,容易被其他电路和其他类型的电路或设备驱动。

下面展示一些 BJT与CMOS。

为什么BJT比CMOS速度要快? 主要受迁移率影响。 以NPN管和NMOS为例,BJT迁移率约为1350cm2/vs。 NMOS半导体表面迁移率约为400-600cm2/vs。 所以BJT跨导高于MOS速度快于MOS。 这也是NPN(NMOS)比PNP(PMOS)快的原因。/pre>NPN比PNP快也是因为载流子迁移率不同,NPN中的基区少子是电子,迁移率大(1350左右);PNP的基区少子是空穴(480左右)。所以同样的结构和尺寸的管子,NPN比PNP快。所以在双极工艺中,是以作NPN管为主,PNP都是在兼容的基础上做出来的。MOS工艺都是以N阱PSUB工艺为主,这种工艺可做寄生的PNP管,要做NPN管就要是P阱NSUB工艺。

BJT是之所以叫bipolar,是因为基区中既存在空穴又存在电子,是两种载流子参与导电的;而MOS器件的反形层中只有一种载流子参与导电。

但并不是因为两种载流子导电总的迁移率就大了。而且情况可能恰恰相反。因为载流子的迁移率是与温度和掺杂浓度有关的。半导体的掺杂浓度越高,迁移率越小。而在BJT中,少子的迁移率起主要作用。

NPN管比PNP管快的原因是NPN的基子少子是电子,PNP的是空穴,电子的迁移率比空穴大。NMOS比PMOS快也是这个原因。

而NPN比NMOS快的原因是NPN是体器件,其载流子的迁移率是半导体内的迁移率;NMOS是表面器件,其载流子的迁移率是表面迁移率(因为反形层是在栅氧下的表面形成的)。而半导体的体迁移率大于表面迁移率。

器件使用建议

1:多余不用输入管脚的处理

在多数情况下,集成电路芯片的管脚不会全部被使用。所有数字逻辑器件的无用端子必须连接到一个高电平或低电平,以防止电流漂移(具有总线保持功能的器件无需处理不用输入管脚)。究竟上拉还是下拉由实际器件在何种方式下功耗最低确定。 244、16244经测试在接高电平时静态功耗较小,而接地时静态功耗较大,故建议其无用端子处理以通过电阻接电源为好,电阻值推荐为1~10K。2:选择板内驱动器件的驱动能力,速度,不能盲目追求大驱动能力和高速的器件,应该选择能够满足设计要求,同时有一定的余量的器件,这样可以减少信号过冲,改善信号质量,对EMI也有一定的好处。并且在设计时必须考虑信号匹配。

3:在总线达到产生传输线效应的长度后,应考虑对传输线进行匹配,一般采用的方式有始端匹配、终端匹配等。

始端匹配是在芯片的输出端串接电阻,目的是防止信号畸变和地弹反射,特别当总线要透过接插件时,尤其须做始端匹配。始端匹配推荐电阻值为10~51Ω,在实际使用中可根据IBIS模型模拟仿真确定其具体值。

终端匹配网络加重了总线负载,所以不应该因为匹配而使Buffer的实际驱动电流大于驱动器件所能提供的最大Source、Sink电流值。

应选择正确的终端匹配网络,使总线即使在没有任何驱动源时,其线电压仍能保持在稳定的电平。

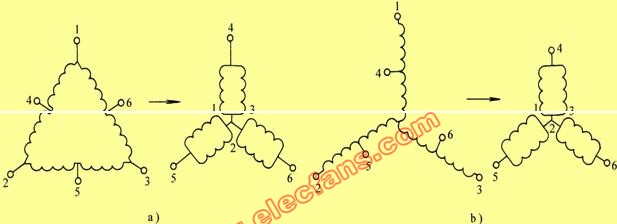

OC/OD门

OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector(Open Drain)。

Open-Drain是对MOS管而言,Open-Collector是对双极型管而言,在用法上没啥区别。

为什么引入OC门?

实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。因此,需要一种新的与非门电路——OC门来实现“线与逻辑”。

OC门主要用于3个方面:

1、实现与或非逻辑,用做电平转换,用做驱动器。由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC.OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

2、线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。在硬件上,可用OC门或三态门(ST门)来实现。用OC门实现线与,应同时在输出端口应加一个上拉电阻。

- 三态门(ST门)主要用在应用于多个门输出共享数据总线,为避免多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

开漏形式的电路有以下几个特点:

a.利用外部电路的驱动能力,减少IC内部的驱动。或驱动比芯片电源电压高的负载。

b.可以将多个开漏输出的Pin,连接到一条线上。通过一只上拉电阻,在不增加任何器件的情况下,形成“与逻辑”关系。这也是I2C,SMBus等总线判断总线占用状态的原理。如果作为图腾输出必须接上拉电阻。接容性负载时,下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢。如果要求速度高电阻选择要小,功耗会大。所以负载电阻的选择要兼顾功耗和速度。

c.可以利用改变上拉电源的电压,改变传输电平。例如加上上拉电阻就可以提供TTL/CMOS电平输出等。

d.开漏Pin不连接外部的上拉电阻,则只能输出低电平。一般来说,开漏是用来连接不同电平的器件,匹配电平用的。

正常的CMOS输出级是上、下两个管子,把上面的管子去掉就是OPEN-DRAIN了。这种输出的主要目的有两个:电平转换和线与。

由于漏级开路,所以后级电路必须接一上拉电阻,上拉电阻的电源电压就可以决定输出电平。这样你就可以进行任意电平的转换了。

线与功能主要用于有多个电路对同一信号进行拉低操作的场合,如果本电路不想拉低,就输出高电平,因为OPEN-DRAIN上面的管子被拿掉,高电平是靠外接的上拉电阻实现的。(而正常的CMOS输出级,如果出现一个输出为高另外一个为低时,等于电源短路。)

当两个与非门的输出全为1时,输出为1;只要其中以输出为0,则输出为0,所以该电路符合与逻辑功能,即L=(AB)’(CD)’。当其他门电路作为OD门的负载时,OD门称为驱动门,其后所接的门电路称为负载门。由于驱动门的输出电容、负载门的输入电容以及接线电容的存在,上拉电阻势必影响OD门的开关速度,RP的值越小,负载电容的充电时间常数也越小,因而开关速度越快。但上拉电阻不能任意的减小,它必须保证OD门输出端的电流不能超过允许的最大值IOL(max)。对于74HC/74HCT系列CMOS电路,IOL(max)=4 mA,因此RP必须大于VDD/IOL(max)=5 V/4 mA = 1.25kΩ 。与普通CMOS电路相比,RP的值比PMOS管导通电阻大,因而,OD门从低电平到高电平的转换速度比普通CMOS门慢。

参考文献

文献 1.

文献 2.

文献 3.

文献 4.