赛灵思7系列FPGA上电配置流程

时间:2023-02-10 23:00:00

一、FPGA配置引脚说明

1、CFGBVS

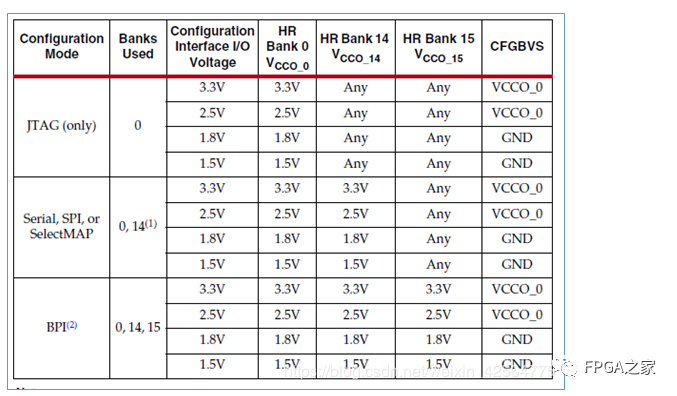

如果VCCO0连接至2.5V或3.3V,CFGBVS连接至VCCO0。

如果VCCO0连接至1.5V或1.8V,CFGBVS连接至GND。

建议bank0、bank14、bank15的VCCO电压一致,避免发生I/O Transition at the End of Startup(建议按下表配置)

2、M[2:0]

根据下表选择模式配置引脚。

3、PROGRAM_B(input)

低电平有效,低时清空配置信息,重新进行配置过程。上电时保持。PROGRAM_B不会使低电平FPGA配置保持复位状态。而是使用INIT_B延迟上电配置序列。

4、INIT_B(inout)

FPGA配置复位,FPGA配置存储器时,或在初始化(清除)FPGA当检测到配置错误时,FPGA将引脚驱动到低电平。上电期间,INIT_B在初始化过程结束时,上电配置序列可以在外部保持低电平。在初始化过程之后INIT_B当输入检测到高电平时,FPGA继续执行M [2:0]引脚设置中指示的配置序列的其他部分。

5、VCCBATT

VCCBATT是FPGA内部易失性存储器的电池备用电源用于存储AES解密器的密钥。如果不需要在易失性密钥存储区域使用解密钥,请将引脚连接到GND或VCCAUX。

二、使用EMCCLK引脚,全速加载程序

由于CCLK引脚有容差,所以可以例CCLK时钟更准确EMCCLK引脚。使这一功能需要以下步骤:

1、使能ExtMasterCclk_en比特流生成选项

2、定义EMCCLK目标电压。Bank 14还有另一个定义IOSTANDARD的引脚。在BANK14上定义的电压自动应用于EMCCLK。使用BITSTREAM.CONFIG.EXTMASTERCCLK_EN属性在Vivado中设置ExMasterCclk_en选项

三、FPGA加载时序

上电时序图

上电时序图

上电配置流程

配置过程分为8个步骤。

1、上电

需要7系列设备VCCO_0,VCCAUX,VCCBRAM和VCCINT引脚供电。上电时,VCCINT必须提供1个电源引脚.0V或0.9V(适用于-2L)电源。在JTAG模式下,除VCCO_0之外的任何I / O不需要7系列电源FPGA配置供电。多功能引脚的配置模式(即串行,主BPI,SPI,SelectMAP)还必须提供时间VCCO_14,VCCO_15或两者。上电后,可以通过将军PROGRAM_B将引脚切换到低电平进行重新配置。

应用:此步可以用来使用看门狗电路重新加载FPGA,或者通过其他设备(DSP、CPLD等)对FPGA控制重新加载。

2.清除配置内存

设备上电后,PROGRAM_B引脚脉冲为低电平JTAG JPROGRAM指令或IPROG配置存储器在命令后或回退重试配置序列期间将被清除。块RAM被复位到其初始状态,并通过断言全局位置复位(GSR)触发器始化触发器。在此期间,除少数配置输出引脚外,使用全局三态(GTS)将I / O如果放置在高阻态中PUDC_B低电平时,内部上拉。INIT_B内部驱动在初始化期间为低电平,然后在TPOR然后用于上电,TPL用于其他情况。如果INIT_B引脚从外部保持低电平,设备将在初始化过程中等待,直到引脚释放并满足TPOR或TPL延迟。

3、采样M2:0引脚

当INIT_B当引脚为高电平时,设备对齐M [2:0]模式引脚采样,如果处于主模式,则开始驱动CCLK。此时,设备开始沿着配置数据输入引脚采样配置时钟的上升。对于BPI和SelectMAP模式,总线宽度最初为x状态寄存器反映了这一点。状态寄存器在总线宽度检测序列后更新。通过重新上下电或PROGRAM_B重新配置位置时,模式引脚将再次采样。

4、同步

对于BPI,Slave SelectMAP和Master SelectMAP必须首先检测总线的宽度。从串行,主串行,SPI和JTAG总线宽度检测模式被忽略。然后必须使用特殊的32位同步词(0xAA99566)发送到配置逻辑。即将到来的配置数据,并将配置数据与内部配置逻辑对齐。忽略同步前输入引脚上的任何数据,除了总线宽度自动检测序列。由于工具生成的所有配置比特流,同步对大多数用户都是透明的(BIT文件)包括总线宽度检测模式和同步字。

同步检测信号

5、检查设备ID

设备同步后,必须先通过设备ID检查可以加载配置数据帧。这可以防止比特流配置不同设备的格式化。若发生在配置期间ID如果出现错误,设备将尝试重新配置回退。设备ID检查内置在比特流中,使这一步对大多数设计师来说都是透明的。器件ID通过比特流中的命令检查到配置逻辑,而不是通过JTAG IDCODE执行寄存器。

ID注解

6、加载数据

加载同步字,检查设备ID之后,将加载配置数据帧。这个过程对大多数用户都是透明的。

7.循环冗余校验

加载配置数据帧时,设备从配置数据包中计算循环冗余验证(CRC)值。加载配置数据帧后,配置比特流可以向设备发出校验CRC指令,然后是预期CRC值。如果设备计算CRC值与比特流的预期CRC设备将值不匹配INIT_B降低并暂停配置。CRC配置比特流中包含默认验证。

加密比特流(当BITSTREAM.ENCRYPTION.ENCRYPT属性为是时),禁用CRC校验,而HMAC验证加密的比特流数据。比特流数据中的错误BOOTSTS寄存器中的报告是HMAC错误。

如果在配置为FPGA在配置主机的模式下CRC错误,则设备可以尝试进行回退重配置。在BPI和SPI在模式下,如果返回重新配置再次失败,则BPI / SPI接口只能通过脉冲PROGRAM_B重新同步引脚,重新开始配置过程。JTAG接口仍然响应,设备仍在移动,只有BPI / SPI接口无法工作。

7系列设备使用32位CRC校验。CRC验证旨在捕捉传输配置比特流的错误。有这样的情况:CRC验证可能会错过比特流传输配置的错误:某些时钟错误(如双时钟)可能导致32位比特流分组和配置逻辑的同步丢失。同步丢失后,不了解任何后续命令,包括检查CRC的命令。在这种情况下,配置是由于DONE Low和INIT_B High而失败,因为CRC被忽略。在BPI在模式异步读取中,地址计数器最终溢出或溢出,导致环绕,从而触发返回重新配置。BPI同步读取模式不支持环绕错误条件。

8、启动

加载配置帧后,比特流指示设备进入启动序列。启动序列由8相(0-7阶段)顺序状态机控制。启动顺序控制程序执行下表中列出的任务。用户可以编程每个启动事件的特定阶段。

可以强行启动序列等待MMCM锁定或使DCI匹配适当的选项。这些选项通常设置在MMCM锁定和/或DCI匹配前阻止DONE,GTS和GWE位置(阻止设备操作)。

DONE在用户指示在用户指示的周期中释放信号,但启动定序器直到DONE引脚实际上看到了逻辑高电平。DONE引脚是泄漏的双向信号。DONE引脚,设备停止驱动逻辑低电平,并通过内部上拉电阻上拉引脚。默认情况下,DONE_PIPE被使能,以在DONE将寄存器添加到引脚和配置逻辑之间。

与启动序列发生器相关的信号

与启动序列发生器相关的信号时序

默认情况下,释放启动第四阶段DONE,并启用DONE_PIPE添加额外的延迟时钟周期。DONE表示配置已完成,所有数据已加载,但需要应用一些额外的时钟周期,以确保启动顺序正确完成到第7阶段,即启动结束。DONE保守4后所需时钟周期的保守数字; 这将解释最常见的用例。比特流选项LCK_cycle或Match_cycle将添加未定义的额外数量的时钟周期。

在Spartan-7,Artix-7和Kintex-如果在7系列中bank的VCCO为1.8V或更低,所以在I / O bank引脚有多功能配置,应该是bank上的引脚是 低或浮动,然后在配置启动期间输入0-1-0过渡到互连逻辑。这种转换发生在GWE内部逻辑启用后,设备的内部状态可能会受到配置后的影响。在EOS(启动结束)后,发生了一个转换CFGCLK。为避免这种转换,将VCCO_14和VCCO_15设置为2.5V或3.3V,或将引脚驱动到外部高电平(见表5-13)。否则,逻辑应该设计为忽略这些受影响的输入信号,直到EOS上升后的一个CFGCLK之后至少200 ns。可以使用STARTUPE2监视CFGCLK和EOS。

四、配置文件格式

烧写配置文件有四种,其中MCS、BIN和HEX文件为固化文件,直接烧写至FPGA存储器中的插件。

五、MultiBoot

7系列FPGA MultiBoot后备功能支持现场更新系统。现场可动态升级比特流图像。FPGA ultiBoot功能可以实时切换图像。在MultiBoot配置过程中检测到错误时,FPGA可以触发回退功能,确保可以将已知良好的设计加载到设备中

发生回退时,内部生成的脉冲会复位整个配置逻辑,但专用的MultiBoot逻辑,热启动开始地址(WBSTAR)和启动状态(BOOTSTS)寄存器除外。该复位脉冲将INIT_B和DONE拉低,清除配置存储器,并从地址0重新开始配置过程,并将修订选择(RS)引脚驱动为00.复位后,比特流将覆盖WBSTAR起始地址。

在配置期间,以下错误可能会触发回退:IDCODE错误、CRC错误、看门狗超时、BPI地址环绕错误。

也可以使用比特流选项ConfigFallback启用后备。在回退重新配置期间忽略嵌入式IPROG。在回退重新配置期间禁用看门狗定时器。如果回退重新配置失败,则配置停止,INIT_B和DONE都保持为低。

六、BPI - 硬件RS引脚设计注意事项

在BPI模式下,RS引脚需要连接到高位地址位,其中一个RS引脚上的上拉电阻连接到高位地址线。使用此硬件实现,系统不包括WBSTAR地址,并且每个图像的比特流选项相同。

默认情况下禁用两用RS引脚。在BPI或Master SelectMAP模式的回退期间,RS引脚驱动为低电平,但在SPI模式期间不会驱动为低电平。对于初始MultiBoot系统,RS引脚分别连接到闪存的高位地址位,并分别通过上拉或下拉电阻绑定为高电平或低电平。上电时,系统将引导至由RS上的上拉电阻和地址线连接定义的高位地址空间。在回退期间,RS引脚驱动为低电平,器件从地址空间0引导.RS引脚应连接到系统定义的高位地址,以允许将完整位文件存储在每个存储器段中。

七、多FPGA JTAG菊花链

看完本文有收获?请转发分享给更多人

NOW现在行动!

推荐阅读

【Vivado那些事】如何查找官网例程及如何使用官网例程【Vivado使用误区与进阶】总结篇【Vivado那些事】Vivado下头文件使用注意事项【Vivado那些事】Vivado中常用的快捷键(一)F4键【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

HDL Designer Series(HDS)介绍

SystemVerilog数字系统设计_夏宇闻 PDF

Verilog 里面,always,assign和always@(*)区别

FPGA上如何求32个输入的最大值和次大值:分治一文读懂TCP/IP!《RISC-V on T-Core》学习笔记新年愿望是什么?先送大家一波开发软件谈谈FPGA(入门)学习的两种方式ZYNQ-迷恋ZYNQ-FPGA开发板资源分享

零基础入门FPGA,如何学习?

点击上方字体即可跳转阅读哟

点个在看 你最 好看