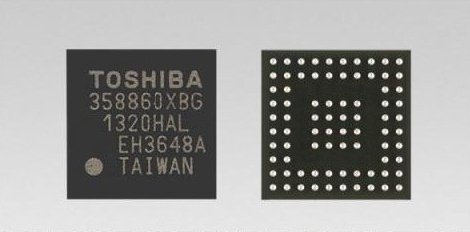

TC358860XBG BGA65 东芝桥接芯片 HDMI转MIPI

时间:2023-01-25 12:30:01

CMOS单晶硅数字集成电路

移动外围设备

概述:

TC358860XBG将嵌入式显示端口(eDPTM)视频流转换为MIPI?DSI流。 在TC358860XBG中有四个eDP主链路通道可在1.62,2.16,2.7,3.24,4.32或5.4 Gbps /在链路上切换,接收高达17.28 Gbps(5.4 Gbps * 0.8 * 4)视频流。 数据通道双链路DSI Tx高达8可发送 Gbps(1 Gbps * 4 * 2)视频流。

对于带宽(BW)<4 Gbps输入视频流,TC358860XBG可通过单个DSI链路输出视频数据,或执行左右线分割,输出双DSI视频数据流链路。 对于BW要求在4 Gbps和8 Gbps之间输入视频流,需要使用左右线分割和双DSI链路使用。

TC358860XBG以2:1的比例提供压缩引擎压缩视频数据。 这使TC358860XBG能够在eDP Rx接收4K @ 60fps视频流压缩并发送到双DSI链路4K显示面板。 在DSI预计面板上会有压缩机。

主机/ eDPTx通过使用其AUX通道(I2C over AUX)控制/配置TC358860XBG芯片。 TC358860XBG主机控制/配置/命令DSI面板提供邮箱注册/命令队列。 主机写入命令队列后,TC358860XBG启动DSI命令包和DSI面板通信。

或者,外部I2C主机可通过I2C总线配置TC358860XBG。 也可以通过命令队列地址I2C总线访问意味着主机可以使用I2C相反,访问命令队列控制DSI面板参数。

请注意,主机不能同时使用AUX ch。 用于设置寄存器I2C总线。

特性:

●TC358860XBG遵循以下标准:

?MIPI联盟规范显示串行接口(DSI)版本1.1,2011年11月22日

?MIPI联盟规范D-PHY版本1.1,2011年11月7日

?VESA DisplayPort标准版1.2a,2012年5月23日。

?VESA嵌入式DisplayPort标准版本1.4 2013年2月28日

●eDP接收器

?比特率@ 1.62,2.16,2.7,3.24,4.32或5.4Gbps,电压摆幅@ 0.2至1.2V,预加重电平@ 3.5dB。

?eDP在1、2或4通道配置中,主链路有四个通道。

?支持单流传输(SST),而不是多流传输(MST)

?能够进行完整快速的链接培训

?标称位速率为1 Mbps的AUX通道。

?支持视频输入数据格式:RGB666和RGB888

?绝对最大像素率为600 Mpixel / s。

?支持替代加扰器种子重置(ASSR)不支持内容保护HDCP加密。

- 系统设计师可以将ASSR_Disable Pad连接到GND,防止eDPTx禁用(源设备)ASSR模式TC358860XBG。

- 换句话说,当ASSR_Disable焊盘接地时,源设备不能接地eDP_CONFIGURATION_SET寄存器(DPCD地址0010Ah,bit 0)的ALTERNATE_SCRAMBER_RESET_ENABLE位清零为0。

?无音频SDP,多点触摸和背光DPCD寄存器支持

?支持24,25,26和27MHz的REFCLK。

●DSI发送器

?双数据通道DSI链路,数据通道0有双向支持。每个链路可用于1、2、3或4数据通道配置。 最大速度为1.0 Gbps /通道。

?无深色支持,视频输入数据格式:RGB666和RGB888

- TC358860XBG对RGB888视频流执行抖动RGB666面板

- TC358860XBG将RGB666视频流(RGB [5:0]?{RGB [5:0],RGB [5:4])的MSB位附加到RGB888面板

?不支持隔行视频模式。

?左右分割的双链路:DSI0携带eDP Rx视频流的左半部分数据,DSI携带右半部分数据

- DSI0可配/编程到DSITx端口。

- 最大长度限制为2048像素和32像素重叠。

- DSI0和DSI1之间的偏移(DSI1延迟到DSI可通过寄存器使用

?为eDP主机/发射器提供控制TC358860XBG以及面板的路径。

?用于验证没有内置彩条发生器eDPRx输入的双DSI链接。

?在eDPRx当端口连续接收视频流时,DSITx以视频模式工作。

●视频功能

?压缩机:2-1压缩4k2k分辨率

?魔方

?彩条输出调试

●I2C从端口

?支持正常(100 kHz),快速(400 kHz或1 MHz,如果SysClk运行在25 MHz)模式。

?外部I2C可访问主机TC358860XBG内部和DPCD读/写寄存器DSI面板寄存器(通过DSI链路)。

?自动增加支持地址。

?TC358860XBG站端口地址为0x68(二进制1101_000x),其中x = 1用于读取,x = 0用于写入。 从机地址可以通过弱上拉电阻改为0x0E(二进制0001_110x),在引导时引脚GPIO0。

●电源

?MIPI D-PHY 1.2 V

?核心,MIPI D-PHY和eDP-PHY 1.1 V

?eDP-PHY:1.8 V

?I / O:1.8 V或3.3 V(所有IO引脚必须具有相同的功率水平)

?HPD输出焊盘1.8 V或3.3 V

●功耗(典型条件)

?126 mW

- 条件:输入5.4 Gbps eDP 1通道,输出DSI端口4数据通道,全高清@ 60fps分辨率,24 bpp

●封装

?65引脚FBGA封装,0.5 mm球距

?5 x 5平方毫米