2021-06-24

时间:2023-01-06 15:00:00

《 DDR系列深度研究

我最近看到的DDR整理相关技术文章,发表一系列文章,尽可能深入全面地介绍不同方面的技术。我希望它能帮助大多数读者。请纠正缺点。

第二篇:DRAM工作原理

1.Storage Capacitor

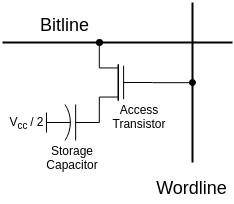

DRAM Storage Cell 使用 Storage Capacitor 来存储 Bit 信息。

从原上,一个是最简单的,存储一个 Bit 信息的 DRAM Storage Cell 如下图所示:

由以下 4 部分组成:

Storage Capacitor,也就是说,存储电容器,它通过存储在电荷中的电荷或电容器两端的电压差来表示逻辑上的 1 和 0。

Access Transistor,即访问晶体管,其导通和截止决定了允许或禁止 Storage Capacitor 读取和重写存储的信息。

Wordline,即字线,它决定了 Access Transistor 导通或截止。

Bitline,即位线是外部访问 Storage Capacitor 唯一的通道,当 Access Transistor 导通后,外界可以通过 Bitline 对 Storage Capacitor 读写操作。

Storage Capacitor 的 Common 端接在 Vcc/2。

当 Storage Capacitor 存储的信息为 1 另一端电压为 Vcc,此时储存的电荷

Q = Vcc/2 / C

当 Storage Capacitor 存储的信息是 0 另一端电压为 0.此时储存的电荷

Q = -Vcc/2 / C

1.1 数据读写原理

从以上结构图分析,很容易推断出来 DRAM Storage Cell 数据读写流程:

1.读数据时,Wordline 打开逻辑高电平 Access Transistor,然后读取 Bitline 上的状态。

2.写数据时,首先将要写入的电平状态设置为 Bitline 上,然后打开 Access Transistor,通过 Bitline 改变 Storage Capacitor 内部状态。

但是,在具体实现中,如果按照上述流程进行 DRAM Storage Cell 读写会遇到以下问题:

1.外界的逻辑电平与 Storage Capacitor 电平不匹配

由于 Bitline 的电容值比 Storage Capacitor 要大得多(通常是) 10 当 Access Transistor 导通后,如果 Storage Capacitor 存储的信息是 1 时,Bitline 电压变化很小。外部电路不能直接通过 Bitline 来读取 Storage Capacitor 存储的信息。

2.读取操作后,Storage Capacitor 存储的电荷会发生变化

在读取过程中,Access Transistor 导通后,因为 Bitline 和 Storage Capacitor 端部电压不一致会导致端部电压不一致 Storage Capacitor 储存在中间的电荷量发生了变化。在下一次读取操作中,最终可能无法正确判断 Storage Capacitor 内存储的信息。

3.由于 Capacitor 即使不进行读写操作,储存的电荷也会逐渐减少

这一特性要求 DRAM 没有读写操作,也要主动 Storage Capacitor 电荷恢复操作。

为解决上述问题,DRAM 介绍了设计 Differential Sense Amplifier。

2. Differential Sense Amplifier

Differential Sense Amplifier 包含 Sensing Circuit 和 Voltage Equalization Circuit 两个主要部分。它的主要功能是将军 Storage Capacitor 存储的信息转换为逻辑 1 或者 0 相应的电压,并呈现到 Bitline 上。同时,读取操作完成后,通过 Bitline 将 Storage Capacitor 电荷恢复到读取前的状态。

在下一节中,我们通过完整的数据读取和写入过程来理解 Differential Sense Amplifier 工作原理。

2.1 Read Operation

一个完整的 Read Operation 包含了,Precharge、Access、Sense、Restore 四个阶段。在后续的小节中,从 Storage Capacitor 读取 Bit 1 完整过程。

2.1.1 Precharge

在这个阶段,首先要控制 EQ 信号,让 Te1、Te2、Te3 晶体管处于导通状态, Bitline 和 /Bitline 在线电压稳定 Vref 上, Vref = Vcc/2。然后进入下一阶段。

2.1.2 Access

经过 Precharge 阶段, Bitline 和 /Bitline 线上电压稳定 Vref 这时,通过控制 Wordline 信号,将 Ta 晶体管导通。Storage Capacitor 存储在中间的正电荷会流动 Bitline,继而将 Bitline 电压拉升到 Vref 。然后进入下一阶段。

2.1.3 Sense

由于在 Access 阶段,Bitline 电压被拉升到 Vref ,Tn2 会比 Tn1 更具导通性,Tp1 则会比 Tp2 更具导通性。

此时,SAN (Sense-Amplifier N-Fet Control) 它将被设置为逻辑 0 的电压,SAP (Sense-Amplifier P-Fet Control) 则它将被设置为逻辑 1 的电压,即 Vcc。由于 Tn2 会比 Tn1 更具导通性,/Bitline 上部电压会更快 SAN 拉到逻辑 0 同理,电压,Bitline 电压也会更快 SAP 拉到逻辑 1 电压。接着 Tp1 和 Tn2 进入导通状态,Tp2 和 Tn1 进入截止状态。

最后,Bitline 和 /Bitline 电压处于稳定状态,正确呈现 Storage Capacitor 存储的信息 Bit。

2.1.4 Restore

在完成 Sense 阶段操作后,Bitline 线路逻辑稳定 1 电压 Vcc,此时 Bitline 会对 Storage Capacitor 充电。特定时间后,Storage Capacitor 读取操作前可恢复电荷状态。

最后,通过 CSL 信号,让 Tc1 和 Tc2 进入导通状态,外界就可以从 Bitline 上读取到具体的信息。

2.1.5 Timing

整个 Read Operation 的时序如下图所示,其中的 Vcc 即为逻辑 1 所对应的电压,Gnd 为逻辑 0。

3. Write Operation

Write Operation 的前期流程和 Read Operation 是一样的,执行 Precharge、Access、Sense 和 Restore 操作。差异在于,在 Restore 阶段后,还会进行 Write Recovery 操作。

3.1 Write Recovery

在 Write Recovery 阶段时,通过控制 WE (Write Enable) 信号,让 Tw1 和 Tw2 进入导通状态。此时,Bitline 会被 input 拉到逻辑 0 电平,/Bitline 则会被 /input 拉到逻辑 1 电平。

经过特定的时间后,当 Storage Capacitor 的电荷被 Discharge 到 0 状态时,就可以通过控制 Wordline,将 Storage Capacitor 的 Access Transistor 截止,写入 0 的操作就完成了。

4.DRAM Memory Organization

为了更清晰的描述 Cells 的组织方式,我们先对上一章节中的 DRAM Storage Cell 进行抽象,最后得到新的结构图,如下:

4.1 Memory Array

DRAM 在设计上,将所有的 Cells 以特定的方式组成一个 Memory Array。本小节将介绍 DRAM 中是如何将 Cells 以 特定形式的 Memory Array 组织起来的。

首先,我们在不考虑形式的情况下,最简单的组织方式,就是在一个 Bitline 上,挂接更多的 Cells,如下图所示:

然而,在实际制造过程中,我们并不会无限制的在 Bitline 上挂接 Cells。因为 Bitline 挂接越多的 Cells,Bitline 的长度就会越长,也就意味着 Bitline 的电容值会更大,这会导致 Bitline 的信号边沿速率下降(电平从高变低或者从低变高的速率),最终导致性能的下降。为此,我们需要限制一条 Bitline 上挂接的 Cells 的总数,将更多的 Cells 挂接到其他的 Bitline 上去。

从 Cell 的结构图中,我们可以发现,在一个 Cell 的结构中,有两条 Bitline,它们在功能上是完全等价的,因此,我们可以把 Cells 分摊到不同的 Bitline 上,以减小 Bitline 的长度。然后,Cells 的组织方式就变成了如下的形式:

当两条 Bitline 都挂接了足够多的 Cells 后,如果还需要继续拓展,那么就只能增加 Bitline 了,增加后的结构图如下:

从图中我们可以看到,增加 Bitline 后,Sense Amplifier、Read Latch 和 Write Driver 的数量也相应的增加了,这意味着成本、功耗、芯片体积都会随着增加。由于这个原因,在实际的设计中,会优先考虑增加 Bitline 上挂接的 Cells 的数量,避免增加 Bitline 的数量,这也意味着,一般情况下 Wordline 的数量会比 Bitline 多很多。

上图中,呈现了一个由 16 个 Cells 组成的 Memory Array。其中的控制信号有 8 个 Wordline、2 个 CSL、2 个 WE,一次进行 1 个 Bit 的读写操,也就是可以理解为一个 8 x 2 x 1 的 Memory Array。

如果把 2 个 CSL 和 2 个 WE 合并成 1 个 CSL 和 1 个 WE,如下图所示。此时,这个 Memory Array 就有 8 Wordline、1 个 CSL、1 个 WE,一次可以进行 2 个 Bit 的读写操作,也就是成为了 8 x 1 x 2 的 Memory Array。

按照上述的过程,不断的增加 Cells 的数量,最终可以得到一个 m x n x w 的 Memory Array,如下图所示

其中,m 为 Wordline 的数量、n 为 CSL 和 WE 控制信号的数量、w 则为一次可以进行读写操作的 Bits。

在实际的应用中,我们通常以 Rows x Columns x Data Width 来描述一个 Memory Array。后续的小节中,将对这几个定义进行介绍。

4.1.1 Data Width

Memory Array 的 Data Width 是指对该 Array 进行一次读写操作所访问的 Bit 位数。这个位数与 CSL 和 WE 控制线的组织方式有关。

4.1.2 Rows

DRAM Memory 中的 Row 与 Wordline 是一一对应的,一个 Row 本质上就是所有接在同一根 Wordline 上的 Cells,如下图所示。

DRAM 在进行数据读写时,选中某一 Row,实质上就是控制该 Row 所对应的 Wordline,打开 Cells,并将 Cells 上的数据缓存到 Sense Amplifiers 上。

Row Size

一个 Row 的 Size 即为一个 Row 上面的 Cells 的数量。其中一个 Cell 存储 1 个 Bit 的信息,也就是说,Row Size 即为一个 Row 所存储的 Bit 位数。

4.1.3 Columns

Column 是 Memory Array 中可寻址的最小单元。一个 Row 中有 n 个 Column,其中 n = Row Size / Data Width。下图是 Row Size 为 32,Data Width 为 8 时,Column 的示例。

Column Size

一个 Column 的 Size 即为该 Column 上所包含的 Cells 的数量,与 Data Width 相同。Column Size 和 Data Width 在本质上是一样的,也是与 CSL 和 WE 控制线的组织方式有关(参考 Memory Array 小节中关于 CSL 的描述)。

4.2. Memory Bank

随着 Bitline 数量的不断增加,Wordline 上面挂接的 Cells 也会越来越多,Wordline 会越来越长,继而也会导致电容变大,边沿速率变慢,性能变差。因此,一个 Memory Array 也不能无限制的扩大。

为了在不减损性能的基础上进一步增加容量,DRAM 在设计上将多个 Memory Array 堆叠到一起,如下图所示:

其中的每一个 Memory Array 称为一个 Bank,每一个 Bank 的 Rows、Columns、Data Width 都是一样的。在 DRAM 的数据访问时,只有一个 Bank 会被激活,进行数据的读写操作。

5. 参考资料

1.Memory Systems - Cache Dram and Disk