BC66F3652研发笔记

时间:2022-10-24 07:30:00

BC66F3652研发笔记

一、产品简介

- E330-915T13S是基于BC66F小体积、低功耗、低成本的3652超高性价比FSK串口模块,收发一体,覆盖9000.125 MHz ~ 932.125 MHz频段。

- 模块支持透传、定点传输模式,支持LDC单点唤醒,软件多级空速可调,多级功率可调,可适用于各种无线传输应用。同时,模块简单易用,无需复杂配置即可快速启动,真正即时使用。

- 下载官方数据手册:BC66F3652数据手册

- 下载官方数据手册:BC3602数据手册

1. 产品主要参数

| 主要参数 | 最小值 | 默认值 | 最大值 |

|---|---|---|---|

| 供电范围 | 3 V | 3.3 / 5 V | 5 V |

| 频段范围 | 900.125MHz | 915.125MHz | 932.125MHz |

| 发射功率 | 4 dBm | 13 dBm | 13 dBm |

| 空中速率 | 2K | 2K | 25K |

| 波特率 | 1.2K | 9.6K | 38.4K |

| 封包长度 | - | 58字节 | - |

| 发射电流 | - | 30 mA | - |

| 接收电流 | - | 7mA | - |

| WOR电流 | - | 7 μA | - |

| 休眠电流 | - | 2 μA | - |

| 最大距离 | - | 1.2 KM | - |

2. 芯片周边特性

MCU特性

● 系统时钟:

? Fsys = 8MHz : 1.9V~3.6V

? Fsys = 12MHz:2.7V~3.6V

? Fsys = 16MHz:3.3V~3.6V

● Flash 程序存储器:8K×16

● 数据存储器:512×8

● True EEPROM 存储器:128×8

● 看门狗定时器功能

● 支持在线应用编程 – IAP

● 22 个双向 I/O 口

● 两个与 I/O 口腔共用外部中断引脚

● 可编程 I/O 口源电流可用于LED 驱动应用

● 时间测量、输出匹配、多个定时器模块PWM 输出和单脉冲输出

● 串行接口模块 – SIM,用于 SPI 或 I2C 通信

● 全双工通用异步收发器接口 – UART

● 软件控制 18 个 SCOM/SSEG 口和 4 个 SSEG 口的 1/3bias LCD 驱动

● 可编程内部参考电压 VR 的 12 个外部通道 12-bit 分辨率 A/D 转换器

● 比较器功能

● 产生固定时间中断信号的双时基功能

● 低压复位功能

● 低压检测功能

● 封装类型:46-pin QFN

RF收发器特性

● 频率带宽:315/433/470/868/915MHz

● FSK/GFSK 调制

● 支持 3 线或 4 线 SPI 接口

● 输入电压范围宽:1.9V~3.6V

● 可编程数据速率:2Kbps~250Kbps

● 可编程 TX 输出功率:高达 13dBm

● 低电流损耗

? Deep Sleep 模式电流 0.4μA,支持数据保存

? RX 电流损耗 ( AGC 开启 & 低数据速率 ) @ 868.3MHz:5.5mA

? TX 电流损耗 @ 868.3 MHz: 24mA @ 10dBm POUT

● RX高灵敏度-118dBm @ 2Kbps 无线数据速率 (868.3MHz)

● 片上 VCO 带内置电路滤波器的小数 N 分频合成器

● 支持低成本 16MHz 晶体振动,内置负载电容

● 可编程数字通道滤波器在各种数据速率条件下实现更好的性能

● AGC ( 自动增益控制 ) 功能实现宽输入范围,高达 10dBm

● AFC ( 自动频率补偿 ) 该功能用于补偿晶振老化引起的频漂

● 片上低功率 RC 振荡器用于 WOR ( 从 RX 唤醒 ) 和 WOT ( 从TX 唤醒 ) 功能

● 物理 TX/RX FIFO 缓冲器:TX 64 字节,RX 64 字节

● Simple FIFO/Block FIFO/Extend FIFO ( 高达 255 字节 )/Infinite FIFO 模式

● 可编程载波检测阈值

● FIFO 模式和Direct 模型支持帧同步识别

● 数据包处理

● ATR ( 自动发送 / 接收 )

● 数据包过滤

3. 芯片结构

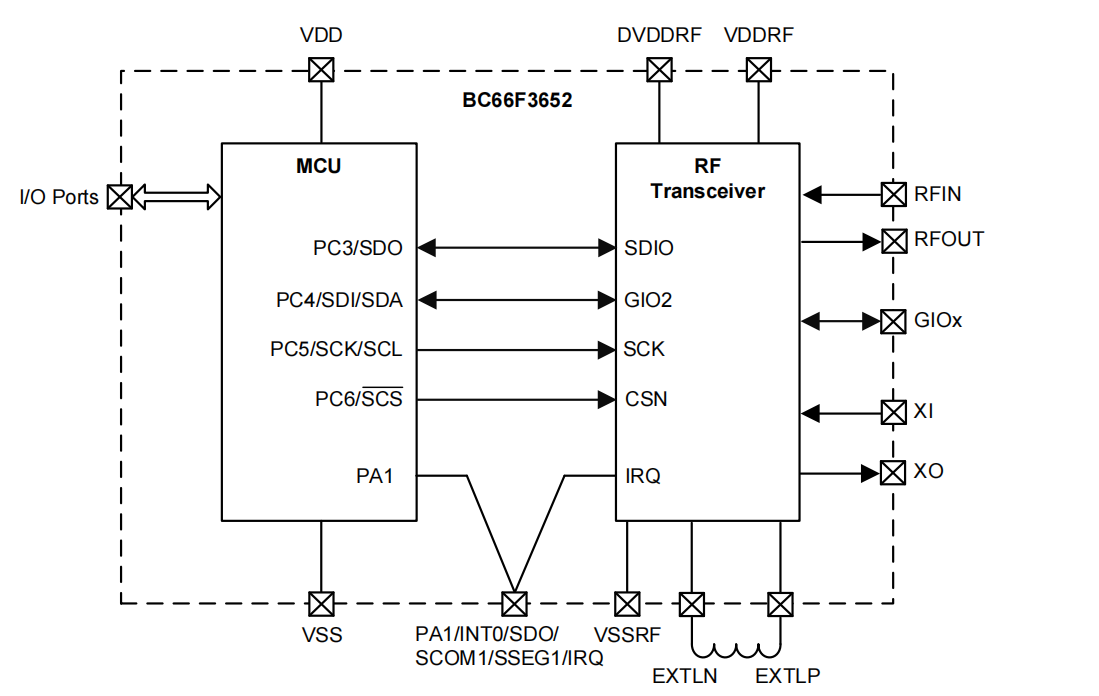

- BC66F3652是一块CHIP IC,内部由HT66F3185和BC3602组成,其IC如图所示:

- 由上图可见,PA1 与 IRQ 也连接过,所以 PA1 中断输入上拉需要设置。

4. 单点唤醒详解

-

E330-915T13S使用的数据封包为:

前导码 Preamble(1) 同步字 SYNC (4) 动态长度 PLEN(1) 数据 DATA(64)

-

不同于其他传统模块,E330-915T13S使用特殊模块的模块WOR唤醒方式:

传统模块在WOR前导码将在模式下发射很长时间,这将导致所有接收模块在一定范围内被唤醒,整个系统之间的功耗将相对较高。

li>

E330-915T13S的单点唤醒则不同(硬件WOR):

其采用短前导码(1)+ 同步字(4)+ 0x00 的格式(空封包),其中 同步字(4)= 短前导码(2)+ 模块地址(2)

当接收到同步字不同时(即模块地址不同),接收方会立即进入IDEL模式不再接收后续的DATA,从而达到省电的效果。

5. 多功能IO口介绍

- BC3602 上搭载了2个多功能IO口,可以配置位于公共区控制寄存器的 IO2 以得到所需的功能:

例如:

- 将BC3602配置为 Direct模式 并将GPIO3/4设置为RXD,可以使用 信号发生器 进行BER的测量。

- 将GPIO3/4配置为TBCLK / RBCLK / LIRCCLK,可以对外部晶振的频偏进行测量。

- 将GPIO3/4配置为 EPA_EN / ELAN_EN 可以判断BC3602当前处于TX或者RX模式。

- Bit 7~4 GIO4S[3:0]:GIO4 引脚功能选择 ( 仅通过 POR 复位 )

0000/0111/1111:无功能,输入

0001:SDO,4 线 SPI 数据,输出

0010:TRXD,Direct 模式 TXD/RXD,输入 / 输出

0011:TXD,Direct 模式 TXD,输入

0100:RXD,Direct 模式 RXD,输出

0101:IRQ,中断请求,输出

0110:ROSCi,ATR 时钟外部输入

1000:TBCLK,TX 位 ( 数据 ) 时钟,输出

1001:RBCLK,RX 位 ( 还原 ) 时钟,输出

1010:FSYCK,即 XCLK 1/1,1/2,1/4,1/8 输出

1011:LIRCCLK,内部 LIRC 去抖时钟,输出

1100:EPA_EN,外部功率放大器使能,输出

1101:ELAN_EN,外部 LNA 使能,输出

1110:TRBCLK,TX 模式的 TBCLK 或 RX 模式的 RBCLK,输出

- Bit 3~0 GIO3S[3:0]:GIO3 引脚功能选择 ( 仅通过 POR 复位 )

0000/0111/1111:无功能,输入

0001:SDO,4 线 SPI 数据,输出

0010:TRXD,Direct 模式 TXD/RXD,输入 / 输出

0011:TXD,Direct 模式 TXD,输入

0100:RXD,Direct 模式 RXD,输出

0101:IRQ,中断请求,输出

0110:ROSCi,ATR 时钟外部输入

1000:TBCLK,TX 位 ( 数据 ) 时钟,输出

1001:RBCLK,RX 位 ( 还原 ) 时钟,输出

1010:FSYCK,即 XCLK 1/1,1/2,1/4,1/8 输出

1011:LIRCCLK,内部 LIRC 去抖时钟,输出

1100:EPA_EN,外部功率放大器 (PA) 使能,输出

1101:ELAN_EN,外部 LNA 使能,输出

1110:TRBCLK,TX 模式的 TBCLK 或 RX 模式的 RBCLK,输出

6. PLL外部电感

- BC3602 锁相环的电感并未集成到IC内部,而是采用了外部电感的方式,所以客户在硬件设计时需要去自行将外部电感调整到合适的电感值:

- PLL的外部电感 在 BC66F3652 的 EXTLN 和 EXTLP 之间(即 PIN11 ~ PIN12 之间),如下所示。

- 除此之外,官方还隐藏了许多寄存器,下图的 VCO Control Register 2寄存器 位于BANK 2的 2CH。

| Name | Addr | R/W | B7 | B6 | B5 ~ B1 | B0 |

|---|---|---|---|---|---|---|

| VC2 | 2CH | RW | DFCSF | VCO_DFC [4:0] | DFC_OW | |

| Reset | 0 | 0 | 1 0 0 0 0 | 0 |

- DFC_OW:

0: VCO_DFC set by channel selection.

(0:通过通道选择设置VCO_DFC)

1: overwrite VCO_DFC by TWIF.

(1:用TWIF覆盖VCO_DFC) - VCO_DFC [4:0]: VCO DFC curve trim value.

(VCO DFC曲线微调值)

- 通过上述寄存器可知:

1. VCO_DFC最大为 31,故需要将 中心频点 的外部电感值调整到靠近 16 ,为其两边的频点保留一定的裕量。

2. 若 VCO_DFC 超过最大值或为零,PLL将无法锁定特定频率,输出的RF波形将会异常。

3. 外部电感附近尽量不要有其他器件,否则波形会被其他器件干扰,导致输出的RF波形会出现尖刺。

读取DFC参考程序:

BC3602_RegisterBank(BC3602_BANK2); //切换为BANK2

VC2 = BC3602_ReadRegister(0x2C); //读取VC2的寄存器值

BC3602_RegisterBank(BC3602_BANK0); //重新回到BANK0

UART_Send(VC2); //将读取到的寄存器值输出到串口

二、各项参数设置

1. 存储器介绍

- 公用区:包含 32 字节空间。无论存储区指针为何值,访问地址 00h~1Fh 都意

味着访问公用区。 - Bank 0~2:每个 Bank 包含 32 字节空间。通过存储区指针选择 Bank。

存储区指针,即 BANK[1:0],定义在公用区,可通过设置寄存器存储区命令直

接设置,且可通过控制寄存器命令进行读 / 写。

2. 输出功率设置

- TX2 寄存器位于 BANK 0 的 3FH

- CT_PAD[3:0]:

输出功率等级,设置为 0x0F 则输出最大功率(13 dBm)

3. 频率设置

- OM 寄存器位于 BANK 0 的 20H

- 设置频段范围:

BAND_SEL[6:5]:

00:315MHz 频段

01:433MHz 频段

10:470~510MHz 频段

11:868/915MHz 频段 - 设置完频段范围后,还需要调整PLL的外部电感值

- 不同的 PCB 需要根据 VCO_DFC 值来判断是外部电感值是否合理

- 不同的元器件电感值也会存在差异

- 参考外部电感值:

315MHz 频段:33nH

433MHz 频段:15nH

470~510MHz频段:13nH

868/915MHz 频段:2.0nH

Note:VCO_DFC 应尽量使靠近中间,避免 VCO_DFC 受 温度 或者 频率范围过大 导致无法锁住特定频率。

- 设置频率:

- SX1、SX2、SX3、SX4位于 BANK 0 的 22H ~25H

- 频率由SX1、SX2、SX3、SX4四个寄存器共同来控制

- 频率计算公式:

D_N[6:0] = floor { fRF / [ fXTAL / ( XODIV2 + 1) ] }

其中fXTAL = 16 MHz(外部晶振频率),fRF为设定频率

D_K[19:0]=floor { ( fRF / [ fXTAL / (XODIV2 + 1) ] - D_N[6:0]) × 220}

例如:

默认 XO = 16 MHz 且 RF 频段 = 433.92 MHz:

→ 433.92MHz / 16MHz = 27.12

→ D_N = 27

→ Dec2Hex(27) = 1B

→ Dec2Bin(27) = 001_1011

→ D_K=0.12×2^20 = 125829

→ Dec2Hex(125829) = 1EB85

→ Dec2Bin(125829) = 0001_1110_1011_1000_0101

∴SX1 = 0x1B,SX2 = 0x1E,SX3 = 0xB8,SX4 = 0x05

4. 数据速率设置

- 数据速率设置:

- MOD1 、MOD2 位于Common BANK 的 14H 和 15H

- 速率由 MOD1、MOD2 两个寄存器控制

- 计算公式:

- RXIFOS[11:0] = floor { fIF / [ fXTAL / ( XODIV2 + 1 ) ] × 217 },XODIV2 = 0

其中 fIF = 数据速率;fXTAL= 16 MHz (外部晶振) - 数据速率 = fXTAL/ [(XODIV2+1)×32×(DTR[8:0] +1)],

→DTR[8:0] = ( fXTAL / 数据速率 -1 ) / 32

数据速率 MOD2 & MOD1的参考设定值:

| 数据速率 | 频率偏移 | MOD2 & MOD1 |

|---|---|---|

| 2K | 8K | 60 F9 H |

| 5K | 20K | 60 63 H |

| 10K | 40K | 60 31 H |

| 25K | 50K | 60 13 H |

| 50K | 18.75K | 60 09 H |

| 125K | 46.875K | 90 03 H |

| 250K | 93.75K | 90 01 H |

5. 频率偏移设置

- 频率偏移设置:

频率偏移由FCF2、FCF3两个寄存器控制

- 计算公式:

- FSCALE[11:0] = round { h × fS / [ fXTAL / ( XODIV2 + 1 ) ] × 215 },

且 h = ( 2 × 频率偏移 ) / ( 数据速率 );

→ FSCALE[11:0] = round { h × 2 / [ fXTAL / ( XODIV2 + 1 ) ] × 215 }, - 其中 fs = 数据速率;fXTAL = 16 MHz (外部晶振)

- FSCALE[11:0] = round { h × fS / [ fXTAL / ( XODIV2 + 1 ) ] × 215 },

频率偏移 FCF3 & FCF2 的参考设定值:

| 数据速率 | 频率偏移 | FCF3 & FCF2 |

|---|---|---|

| 2K | 8K | 00 21 H |

| 5K | 20K | 00 52 H |

| 10K | 40K | 00 A4 H |

| 25K | 50K | 00 CD H |

| 50K | 18.75K | 00 4D H |

| 125K | 46.875K | 01 19 H |

| 250K | 93.75K | 02 94 H |

6. 数据包格式设置

-

数据包格式由 PKT1 ~ PKT9 控制

-

PKT1 ~ PKT9 位于 Common BANK 的 0B H ~ 13 H

-

TXPMLEN[7:0]:TX 前导码长度

发送前导码长度 = (TXPMLEN[7:0]+1) 字节 -

RXPMLEN[1:0]:RX 前导码检测长度选择

00:0 字节 – 无前导码检测

01:1 字节

10:2 字节

11:4 字节 -

SYNCLEN[1:0]:TX/RX 模式同步码长度选择

00:保留 ( 2 字节 )

01:4 字节

10:6 字节

11:8 字节 -

TRAILER_EN:连接码字段使能(复位默认使能)

0:除能

1:使能 -

PLH_EN:有效载荷头码域使能

0:除能

1:使能 -

PLLEN_EN:有效载荷长度域使能(动态长度)

0:除能

1:使能 -

CRC_EN:CRC 域使能

0:除能

1:使能 -

TXDLEN[7:0]:

TX 数据长度 ( 单位:字节;仅用于 Burst 模式 ) -

RXDLEN[7:0]:RX 数据长度 ( 单位:字节;仅用于 Burst 模式 )

当 PLLEN_EN 位清零时,接收的数据长度取决于此字段。

当此寄存器被读取时,所读出的数值表示 RX FIFO 中的数据长度。

此寄存器被读取出的默认值是 00 H。

7. 晶振负载CL设置

- XO1位于 BANK0 的 3EH

- XO_TRIM[4:0]:XO 负载电容微调