用于提高开关电容器电路良率的基于公共质心的单元电容器的最佳布局

时间:2022-09-04 00:00:00

摘要

良率定义为电路在容差范围内符合设计规范的概率。 相关系数高的布局失配少,电容比变化小,从而达到更高的良率性能。 本研究提出了一种新的优化标准,可以快速确定放置是否最好。 导致优化标准 C 条目和分区阵列概念的发展可以显著减少在足够大的阵列大小中寻找最佳/接近最佳位置的搜索空间。

背景

随着半导体技术的不断缩小,工艺变化问题不可避免。 预计工艺变异的不可控问题将变得更加严重。 因此,工艺变化造成的良率损失成为一个重要的设计问题。 将工艺变异带入早期设计阶段,必须将工艺变异信息注入电路模拟器。

工艺角通常考虑在电路仿真中。 利用设备工艺边界模拟良率损失。 但设备边界通常不是性能边界。 表演空间可能在角落空间内或超过角落空间 [Luo et al. 这将导致过度杀伤或超车。 蒙特卡罗分析通常用于提高良率分析的准确性。

调研

设备失配可归因于随机失配和系统失配两个错误来源 [Liu et al. 2008]。 随机失配通常是由工艺变化引起的; 另一方面,系统不匹配主要是由不对称布局和处理梯度引起的。 许多模拟集成电路的关键性能,如模数转换器 (ADC) 与准确的电容比直接相关 [McNutt 等人。 1994]。 使用并联单元电容可以缓解电容比失配问题 [Khalil 等人。 通过常见的纹理结构,可以进一步提高单位电容阵列的精度[Khalil et al。 2005; 哈利勒和德苏基 2002; 马等人。 2007; 黑斯廷斯 2000]。 在制造过程中,梯度和随机误差的影响显著降低。

公共质心结构中的完美匹配装置必须满足以下四个条件 [Hastings 重合、对称、分散和紧致。 为了引导设计师开发适当的布局,制定了许多布局规则,以满足这些条件 [Khalil 等人。 2005; 哈利勒和德苏基 2002; 马等人。 2007; 黑斯廷斯 2000]。 但布局形状必须是矩形才能满足这四个条件。 此外,如果不实施耗时的良率评估过程,通常很难确定哪些条件可以实现更好的匹配 [Chen et al. 2009、2010; 罗等人。 2011]。

事实上,设备之间有一些高度依赖于其空间位置的相关性[Xiong et al。 2007; 多赫等人。 2005]。 近距离设备通常具有类似的参数变化。 表明相关系数高的布局失配少,电容比变化小,良率性能高 [Luo et al. 2008]。 Chen等人提出优化标准。 [2010] 以最高/接近最高相关系数的最佳/接近最佳布局,快速生成两个电容器或连续电容器(多个电容器)的比率。 该算法已成功应用于电荷再分配 (CR) 接近寄存器 (SAR) 模数转换器 (ADC) 提高良率的设计 [Lin 等人。 2011]。 最佳/接近最佳位置,无需蒙特卡罗模拟。

但是,陈等人的优化标准。 [2010] 和林等人。 [2011] 过于简单化了。 较高的相关系数导致较低的比率方差可能并不总是正确的。 使用皮尔逊相关系数 [Chen et al. 定义优化标准过于乐观。 以后会给出反例来解释矛盾。 另一方面,Lin 等人优化标准。 [2011] 仅考虑 R 最大化,即任何单位电容器之间的相互关系数之和。 还将提供反例,以表明它很大 R 值的放置可能并不总是导致较小的标准偏差或较小的方差。 这导致了一种新的优化标准的发展,可以快速有效地识别更好的位置。 蒙特卡洛模拟确认了最终放置。 基于优化标准,开发了一个简单有效的布局生成过程。

下一节将简要回顾空间相关性对产量分析和空间校正模型的影响。 此外,提出了优化准则[Chen et al. 2010; 林等人。 2011] 也进行了讨论。 第 3 本节介绍了建议的优化标准。 第一,基于优化标准 4 讨论了电容器放置的生成。最后,第 5 结论评论很短。

主要方法

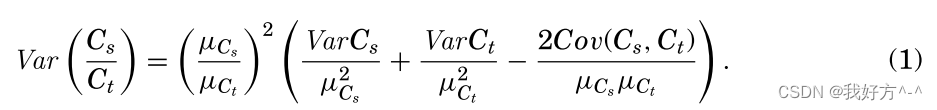

令 μCs 和 μCt 分别是两个电容器 Cs 和 Ct 的标称值。 Var(Cs)和Var(Ct)它们的方差,Cov(Cs,Ct)是协方差。 电容比的变化 Var(Cs/Ct) 表示如下 [Luo et al. 2008]。

让 Cs 和 Ct 分别用 p 和 q 单位电容器 (UC) 实现,即 Cs ={Cs1, Cs2,…,Csp} 和 Ct ={Ct1, Ct2,…,Ctq}。 比率为 Cs : Ct = p : q。 不失一般性,将 (p q) 个 UC 放置在 m×n 在阵列结构上。 自相关 ρs(i, j) 和 ρt(i, j) 分别表示 Csi 和 Csj 之间、Cti 和 Ctj 相关系数和相关系数 ρst(i, j) 它们之间的相关系数 Csi 和 Ctj [罗等人。 2008]。 令Scs和Sct分别为Cs和Ct的总自相关系数之和,Scst是相互关系数之和,即

基于方程式。 (5)罗等人总结了以下性质。 [2008] 相关系数较高 ρcst 导致较小的 Var(Cs/Ct)。 由于电容比的方差越小,通常会导致良率越高,因此相关系数越高,良率越高。 因此,Chen 等人使用相关系数 ρcst。 [2010] 快速确定哪种布局可以在不执行耗时的情况下实现更高的良率性能 Monte-Carlo 模拟。

处理连续比率 C1:C2:…:CN,最近提出了多个电容器的比例 [McNutt 等人。 1994; 哈利勒等人。 2005; 哈利勒和德苏基 2002; 马等人。 2007]; 提出了基于空间相关性的有效电容器放置方法[Chen et al。 2010] 并实施到 SAR ADC 的设计 [Lin et al. 2011]。 更具体地说,设置 ρij 是一对电容器 Ci 和 Cj 相关系数。 最大限度地发问题,最大化 R [Chen et al。 2010],其中

具有最大 R 的 UC 布局将是最佳或接近最佳的布局。

优化标准

我们首先介绍了用于检验 Chen 方差分析等人的优化标准。 [2010] 和林等人。 [2011] 一对电容比和连续电容比。 然后,[Chen et al. 两个标准的反例。 2010; 林等人。 如图所示。 最后,对蒙特卡罗的模拟结果提出了新的优化标准。

图 1 显示了一个 CR-SAR-ADC [Lin 等人。 由电容阵列、比较器和控制单元组成。 考虑一个包含电容器的 Ci, i = 0, 1,… , N 的 N 位 SAR ADC。电容比为 C N : C N ? 1 : . . . : C 2 : C 1 : C 0 = 2 N ? 1 : 2 N ? 2 : . . . : 2 : 1 : 1 C_N : C_{N?1} : ... : C_2 : C_1 : C_0 = 2^{N?1} :2^{N?2} : ... :2:1:1 CN:CN−1:...:C2:C1:C0=2N−1:2N−2:...:2:1:1

令 C∗ i 表示除 Ci 之外的所有电容的总和,i = 1, 2,…, N。

示例 1. 考虑展示位置 [Lin et al. 2011] 在图 2(a) 和 2(b) 中,连续比率 C4:C3:C2:C1:C0 = 8:4:2:1:1。 单位电容Cu为100 fF,单位电容标准差为10 fF,单位相关系数ρ0为0.9。 可以生成一个 16×16 的相关系数矩阵 [Luo et al. 2008]并计算电容的方差和协方差。 对于图 2© 中的布局,C∗ 4 = C0 + C1 + C2 + C3 和 CTotal = C4 + C∗ 4。 (2),我们得到 Var(C4) = Var(C∗ 4) = 5228.5,Cov(C4, C∗ 4) = 5186.6。 通过方程式。 (3)、方差比 Var(C4/CTotal ) = 8.1913e-6。 因此,标准偏差为 Std(C4/CTotal) 为 0.0029。 类似地,可以计算 C1/CTotal 、 C2/CTotal 和 C3/CTotal 的标准差,以及展示位置的 R 值,如表 I 所示。 C1/CTotal 、 C2/CTotal 、 C3/ 的平均值 CTotal 和 C4/CTotal 分别为 0.0625、0.125、0.25 和 0.5。 请注意,为简单起见,系统失配被忽略,因为阵列尺寸很小,并且具有偶数个单元电容器的电容器(C2、C3、C4)具有共同的中心点。

类似地,可以推导出其他布局的标准差,如表 I 所示。结果表明,图 2(a) 和 2(b) 中的两个布局的 R 值都高于图 2© 中的 R 值,因此 是最高有效位 (MSB) 的标准偏差,即 C4/CTotal 。 当位数增加时,情况变得很重要。

为了确认表一中计算值的正确性,进行了蒙特卡洛(MC)模拟来计算方差。 对于 10,000 个样本,模拟结果列于表 II。

让 Cs 和 Ct 用 4 和 26 个单位电容器来实现,它们放置在 6×5 阵列结构上,即 p = 4 和 q = 26,图 3 显示了三种不同的位置,相关的值在表 III 中计算和列出 , 其中 μCu = 100 fF, σCu = 10 fF 并且假设 ρ0 = 0.5。 结果表明,图 3(b) 中的放置导致最高的相关系数 ρcst 和最低的比率方差 Var(Cs/Ct)。 这表明相关系数较高的位置会导致比率的方差较低 [Luo et al. 2008]。

然而,安置在图3 (a)和3 ©,前者有ρcst低于后者,由结论(罗et al . 2008年)前的方差比率应该高于后者。表三示,前者有较低的Var (Cs / Ct)。这与罗的结论et al相悖。[2008]。事实上,获得更高的ρcst, Eq。(5)条款(p + 2 scs)∗(q + 2 sct)必须减少,和术语Scst应该增加。此外,获得较低的Var (Cs / Ct), Eq。(3), (p + 2 scs)和(q + 2 sct)必须降低,Scst应该增加。两种情况下可能不是线性相关的。因此,标准可能不总是对的。为了进一步验证仿真结果的例子,10000个样本的MC模拟是采用各种ρ0,如图4所示。

优化标准

本小节介绍了建议的优化标准。

属性 2. 让 Cs 和 Ct 分别用 p 和 q 单位电容器实现,并且让 (p + q) 单位电容器完全放置在 n×m 阵列上。 总和是这个数组上 (p + q) 个单元的任何位置的常数。

示例 2. 考虑图 5(a) 和 5(b) 中的两个不同位置,其中 p = q = 4 在 2×4 数组结构上。 它们的相关矩阵分别如图 5© 和 5(d) 所示。

基于图 5 中的相关矩阵,两种情况的相关系数可以表示如下。

设 k(a) 为图 5© 中矩阵所有项的系数和,则

证明(属性 2)。 如果两个布局有相同数量的(p+q)个单元电容放置在同一个阵列上,则它们对应的相关矩阵具有置换关系,即一个矩阵可以从另一个矩阵的置换得到。 因此,两个矩阵中所有条目的相关系数的总和是相同的。

基于属性 2,一个新的优化准则可以概括为以下属性。

属性 3. 给定一个 n×m 阵列,电容器 Cs 和 Ct 分别包含 p 和 q 单位电容器。 在同一阵列上的布局中,具有较低 ω 值的布局将导致比率变化较小,

属性 4. 令 p = 1,产生一个布局,即 Cs 的唯一一个单位电容器放置在阵列的 C-entry/C-entries 上,而 Ct 的 q 个单位电容器放置在其余的 数组的条目。 然后,该布局导致同一阵列上的布局之间的比率变化最小。

对于 p = 2,令 (r1, s1) 和 (r2, s2) 为 Cs 的两个单位电容器在 2R×2C 阵列上的位置。 通过方程式。 (17),我们得到

考虑 p = 2 的 8×8 数组。我们将数组划分为两个 8×4 子数组,如图 7(a) 所示。 Cs 的两个单位电容器将分别放置在两个子阵列的 C 条目上,用黄色标记。 类似地,对于 p = 4,令 (ri, si), i = 1,2,3,4 为 Cs 的两个单位电容器在 2R×2C 阵列上的位置。 通过方程式。 (17),请注意,分区子阵列是正方形或矩形。 对于C-entries,放置符合紧致、对称和分散的规则。如果选择靠近中心的C-entries,则放置符合重合规则。将两个单位电容器放置在两个子阵列上,每个子阵列有四个条目,将产生 16 种组合,称为候选放置。 这表明最佳位置的搜索空间从 2-out-of-64 的数量显着减少,C(64,2) = 2016 到 C(4,1)*2 = 16,对于 8- by-8 数组。 事实上,由于阵列的对称性,这 16 个候选布局只能分为六个不同的布局,如图 8 所示,其中放置了 p = 2 个单位电容器

通过方程式。 (18),我们可以很容易地发现图 8(a) 和 8(d) 中的放置具有相同的值 [f(r1, s1) + f(r2, s2)]。 然而,图 8(d) 中的 Scs 比图 8(a) 中的低,因此导致 ω2 较低。 类似地,对于图 8(b) 和 8(e) 中的放置对以及图 8© 和 8(f) 中的放置对,图 8(e) 中的放置(图 8(f))具有较低的 ω2 比图 8(b)(图 8(c))。 此外,两个单元电容放置在距离较远的位置也会导致Scs较低。 图 8(d)-8(f) 中的放置符合公共质心的分散和对称规则。

图 9(a) 显示了所有可能布局的曲线族。 最佳位置是图 8(f) 中的位置。 图 9(b) 将放置的比率方差与图 8(d)-8(f) 中的模式进行了比较。 结果表明,图 8(d) 是 ρ0 =0 到 0.5 的最优解,而图 8(e) 是 ρ0 > 0.8 的最优解。 因此,图 8(d)-8(f) 中的候选布局是取决于 ρ0 值的最佳/接近最佳解决方案。

类似地,图 10(a) 显示了一个 4×4 阵列,该阵列被划分为四个子阵列。 图 10(b) 说明了一个候选位置。 图 10© 绘制了对于将 p = 4 放置到这个 4×4 数组的所有可能放置,ρ0 = 0 到 1 的比率的方差。 结果表明,图 10(b) 中的候选位置是最佳解决方案。

结论

良率定义为所考虑的电路在容差范围内符合设计规范的概率。 然而,在实践中,一个电路通常包括几个设计变量,当考虑到工艺变化时,这些设计变量被视为随机变量。 因此,随机变量的方差可能会影响电路良率。 相关系数较高的布局具有较少的失配和较小的电容比变化,从而实现更高的良率性能。 本研究提出了一种新的优化标准,该标准可以显着减少为足够大的阵列尺寸寻找最佳/接近最佳解决方案的搜索空间。 应该提到的是,结果阵列的可路由性也是一个需要解决的重要问题。 Huang等人提出了一种简单的路由方案。 [2011]; 然而,为了进一步提高良率,正在开发系统地考虑电容器阵列的布局和布线。

尽管前面的讨论将重点放在 2R×2C 数组上,但 C 项的概念可以应用于任何数组大小。 正在开发一个简单而有效的自动布局生成过程 [黄要出现],其中正在实施分区和合并方案以满足重合、分散、对称和紧凑的规则。

值得跟进

- 公共质心结构中的完美匹配器件必须满足以下四个条件 [Hastings 2000]:重合、对称、分散和紧致。[HASTINGS, A. 2000. The Art ofAnalog Layout. Prentice Hall, Upper Saddle River, NJ.]

- 该算法已成功应用于电荷再分配 (CR) 逐次逼近寄存器 (SAR) 模数转换器 (ADC) 设计,以提高良率 [Lin 等人。 2011]。 无需蒙特卡罗模拟即可生成最佳/接近最佳位置。[LIN,C.-W.,LIN,J.-M.,CHIU,Y.-C.,HUANG,C.-P., AND CHANG, S.-J. 2011. Common-centroid capacitor placement considering systematic and random mismatches in analog integrated circuits. In Proceedings ofthe 48rd Annual Design Automation Conference. 528–533.

- 简单的route模式 HUANG,C.-C.,CHEN,J.-E.,LUO,P.-W., AND WEY, C. L. 2011. Yield-aware placement optimization for switched-capacitor analog integrated circuits. In Proceedings of the 24th IEEE International SOC Conference.170–173. DOI: http://dx.doi.org/10.1109/SOCC.2011.6085127.

- 分区和合并 HUANG, C.-C. To appear. Common-centroid-based unit capacitor placement generation for switched-capacitor integrated circuits, Ph.D. dissertation, Department ofElectrical Engineering, National Central University, Jhongli, Taiwan.