18、ADS使用记录之超宽带功放设计

时间:2022-09-28 16:30:00

18、ADS超宽带功放设计使用记录

基于CGH40010F

下载源文件

1.设计指标和实际结果

频率范围:1.4Ghz–2.2Ghz

输出功率:10w(40dbm)

回波损耗小于-15db

漏极效率大于70%

TOI/IP3:-45dbm

2.数据手册分析

我们都开始做超宽带看数据手册。

番外1:射频功放晶体管的重要参数

3、直流分析 选择静态工作点

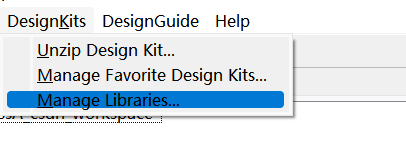

导入CGH40010F第一次使用解压模型文件Design Kit,如果不是第一次使用,可以选择管理库文件。这不是我第一次使用它:

选择添加库定义文件:

找到模型解压的根目录defs文件,点击打开导入库:

新原理图命名01_DC_SIMULATION(本原理图用于直流扫描):

选择菜单栏Insert,插入模板:

我自定义的模板插入在这里:

插入后如下所示(一般插入模板也需要根据数据手册设置相应的电压,此处已设置插入模板,如此处的扫频参数):

点击模拟观察结果:

选择界面移动相关数据mark改变电路的工作状态,选择漏极电压28V、栅极电压-2.8V。从图中可以清楚地看出,此时的导角为232度,按照AB工作效率最高可达近50%。

4.稳定性分析

新原理图命名为02_STABILITY_SIMULATION,插入稳定性分析控件:

对此原理图进行模拟,得到结果,可见使用该稳定电路系统可在频带内实现稳定:

5.负载牵引和源牵引

负载牵引和源牵引在设计中非常重要。二次谐波最高牵引在这里。本设计的通带范围为1.4Ghz-2.2Ghz,在1.4G、1.8G、2.2G牵引三个频率点。

首先,负载牵引,新原理图,命名03_LoadPull_1.4Ghz:

打开负载牵引模板,插入设计中使用的晶体管和外围电路,插入后如下:

相应修改变量框中的数据,将输入功率修改为28dbm,因此,放大后可达近40dbm(10w)偏置电压的输出功率和值由之前的直流分析得出:

模拟按钮修改后,得出以下结果:

观察右下角的功率图,移动marker输出阻抗为18.252 j19.05可以获得最高效率,从而确定1.4Ghz负载牵引值为18.252 j19.05。

新原理图命名03_SourcePull_1.4Ghz,插入源牵引模板:

br> 在其中插入此次设计使用的晶体管和相关的外围稳定电路:

修改参数与此次设计参数一致:

在原理图的右下角填入相关的基波负载阻抗数值:

点击运行仿真:

由图中可观察出源阻抗高效率处,此处取7.4+j*1作为高效率源阻抗。与高效率负载阻抗区域相比高效率源阻抗区更大,更容易匹配。此处可以再将得到的基波阻抗值带入负载牵引原理图进一步仿真,此处就不进行这一步骤了。

按照如上的步骤分别对三个频率点进行牵引,此处就不多赘述了,直接放出结果。

1.8Ghz负载牵引结果为:

1.8Ghz源牵引结果为:

2.2Ghz负载牵引结果为:

2.2Ghz源牵引结果为:

此处还可以对二次谐波进行牵引,详细步骤可以参考番外5:ADS功放设计之负载牵引与源牵引。一般情况下二次谐波高效率空间往往在smith圆图边缘达到,此处就不进行二次谐波牵引了,直接将二次谐波匹配至纯电抗区域(偷个懒)。

可以看到所选的频率点在18.252+j*19.05这个负载阻抗区域具有比较高的效率,因此选取此阻抗点作为宽带匹配点。所选频点的源阻抗在实轴负半区域具有高效率,选取阻抗点18欧姆作为源阻抗。

(在超级超级宽带设计时或者在某些特殊情况时,最佳功率点随频率会有较大的改变,而不会像此处一样变化很小,这个时候就需要匹配到某一高效率区域,而匹配到某一高效率区域是宽带功放更为一般的方法)

6、输出匹配与输出匹配测试

宽带偏置电路

在进行输入和输出匹配前需要先进行偏置电路设计,新建原理图:

在偏置电路设计时,往往采用四分之一波长阻抗变换器的设计方法,这种设计方法频带较窄,会影响输出和输入匹配的带宽,此处采用扇形微带线设计方法:

使用参数自动调整OPTIM,运行结束后得到结果;

可以看到此电路对射频信号具有较好的抑制作用,端口损耗也比较小,适合作为宽带匹配电路的偏置。

谐波控制网络

谐波抑制网络往往用于将高次的谐波匹配到Smith圆图外围以提升效率,功放漏极输出端往往最先连接谐波控制网络,随后才是偏置和基波输出匹配。此处设计的电路频段为1.4-2.2Ghz,因此二次谐波范围为2.8-4.4Ghz。

新建原理图,命名为04_Harmonic_Control_Net:

构建如下的谐波控制网络:

点击进行调谐与参数调整,最终得到如下结果,可以看到该匹配网络能够较好的把二次谐波匹配至圆图边缘,系统呈现低通特性,符合设计要求:

基波匹配电路

此处需要将阻抗从18.252+j*19.05匹配到50欧姆,新建原理图,命名为04_OutputMatch_Smith,插入相关控件:

设置Smith圆图控件如下所示:

进入匹配界面,使用等Q圆0.4进行匹配,使用L型匹配电路:

设计完成后建立ADS电路,运行仿真,得到匹配电路性能图如下所示,性能较好符合设计要求:

上述设计使用的是理想微带线,我们需要将其转换为实际电路;

对此原理图设置目标,进行optim,得到如下结果:

可以看到1.4-2.2Ghz被匹配至高效率区域,二次谐波都位于圆图边缘,达到高效率条件,高效率区域由之前负载牵引得出,在此再次展示一遍:

下面进行输出匹配电路的实际测试,新建原理图命名为04_OutputMatch_Test_HB,设置原理图如下所示:

可以对原理图进行Optim以获取更高的输出效率,此处放出参数调整后的结果,由此可见该电路在1.8Ghz时可以达到百分之78的漏极效率:

对此电路进行频率扫描,发现通带内漏极效率差不多在百分之70以上,性能还算不错:

7、输入匹配与输入匹配测试

输入匹配需要将50欧姆匹配至18欧姆左右,使用Smith圆图构建初步的电路图:

使用Smith圆图进行设计,采用等Q圆图的方式设计宽带的匹配网络:

产生的电路图如下所示:

对此电路图进行测试,得到结果如下所示,表明其具有良好的宽带性能:

在原有电路的基础上将其转换为实际的微带参数电路,并加入之前设计好的偏置电路:

到此输入匹配电路设计完毕,因此构建如下的输入匹配测试电路图:

对此原理图进行调谐后仿真,得到如下结果:

可以看到通带内效率较好,输入匹配性能还算不错。

8、输入匹配和输出匹配测试

构建如下的整体测试电路图:

对此原理图进行optim和仿真,得到如下的结果:

可以看到电路在1.4G-2.37Ghz之间漏极效率大于百分之70,性能较好。

9、版图仿真

待续

版图仿真难调啊