基于FPGA的PCIE设计(1)

时间:2022-09-21 22:00:01

PCIE简介

PCI Express 用于互联计算机和外围设备高速接口总线,可应用于移动设备、台式电脑、工作站、服务器、嵌入式电脑和通信平台等。

PCIe两个设备之间可以实现点对点通信串行通信,如果多台设备需要通过交换器(Switch)这样一个系统就可以连接多个设备。

PCIe作为处理器系统的局部总线,总线起着作用和作用PCI总线类似,当然,主要目的是连接处理器系统中的外部设备PCIe总线也可以连接其他处理器系统。在不同的处理器系统中, PCIe实现系统结构的方法略有不同。但在大多数处理器系统中,它被使用RC、 Switch和PCIe-to-PCI桥连接这些基本模块PCIe和PCI设备。在PCIe基于总线PCIe总线设备,又称EP(Endpoint)。

在计算机通信平台中 , PCI Express系统结构代表高性能外围组件的互联方法

1、 由PCI 和PCI-X 系统结构演变而来architectures

2、 PCI Express 两串行点对点的方式连接两个设备

3、 基于数据包协议实现信息传输

4、 PCI Express 单通道或多通道的数据传输可以在互联网中实现

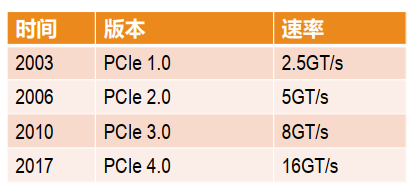

5、 PCI Express 协议已经发布了四个版本

PCIE特点如下:

1.点对点传输

2、 串行总线意味着少用引脚

3、 可选择通道数: x1, x2, x4, x8, x12, x16, x32

4、 全双工通信

5、 2.5Gbps / 5.0Gbps

6、 基于数据包的传输协议

在计算机系统结构中PCIe的应用架构如下:

从上面我们可以看出PCIE应用架构主要包括四个部分:

1、FSB总线CPU交互总线:FSB总线(Front Side Bus)是CPU和DDR内存交互总线

2、Root Complex:RC (Root complex)是PCIe结构体系中的一个重要的结构部件, RC的提出跟X事实上,86系统架构是密切相关的x86架构中有标准RC在其他系统中,没有标准定义RC所有功能。例如X包括86架构DDR控制器和FSB to PCIe的桥, 而ZynqSoc包括芯片架构AXI to PCIe的桥和DDR控制器,PowerPc只包含一个PCIe总线控制器。这里需要注意Root complex包括root port。

3、PCIe Switch:Switch PCIe链路通过Switch扩展链路

4、PCIe End point:即常见的PCIE终端设备,FPGA最常用的也是End point。

FPGA在PCIE中可以成为Root Complex、Switch和 End point:

PCIe总线层次结构主要包括事务层、数据链路层和物理层三层。

1、事务层:PCIe总线层次结构的最高层高层次PCIe设备核心层的数据请求,并将其转换为PCIe总线事务, PCIe这些总线事务用于总线TLP头中定义。PCIe总线使用的数据报文首先在事务层形成, 这份数据报也叫事务层数据报

文,即TLP。(解释:主要意思是事务层将数据封装成TLP包发给下层使用)

2、数据连路层:TLP通过数据链路层添加Sequence Number前缀和CRC后缀,然后发送到物理层。

3、物理层:PCIe电PCIe在链路正常工作之前,需要正确工作PCIe链路训练将在此过程中使用。

LTSSM状态机。LTSSM全称是Link Training and Status State Machine。这个状态机在PCIe在总线的物理层中。状态转移图如下:

Detect状态是PCIe链接训练的开始。 Detect,顾名思义,检测工作需要实现。因为在这种状态下,发送端TX接收端需要检测RX如果检测正常,是否存在并能正常工作才能进入其他状态。RX逻辑是否存在相对简单,即通过一个Detect logic”电路比较RC时间常数的大小。

从上图可以找到PCIe在终端连接上,时间常数会增加。多以决定Detect状态是否进入下一个状态。

Polling 状态的目的是"对暗号",实现无障碍沟通。 TX和RX之间发送TS1、 TS2 OS序列来确定Bit Lock, Symbol Lock以及解决Lane极性反转的问题。

Bit Lock: 在Bit在传输过程中, RX PLL锁定TX Clock这个过程称为频率RX实现"Bit Lock。(解释:即位同步)

Symbol Lock: RX端串并转化器知道如何区别一个有效的10-bit Symbol,这个过程被称为这个过程Symbol Lock”. 这里用的是COM控制符(解释:即帧同步)

常见的视频方案如下:

FPGA中PCIE的实现:

1、7系列FPGA支持实现Gen1与Gen2的PCIE协议

2、Virtex-7 FPGA支持实现Gen3的PCIE协议

3、UltraScale与UltraScale 支持Gen3的PCIE协议

4、支持x1,x2,x4,x8,x16lanes的通路

5、PCIE使用了硬核GTP接口用于串行传输数据

PCIE传输速度如下:

FPGA中PCIE总体框图如下:

1、该硬核PCIE支持Endpoint和Root Port

2、支持AXI4-Stream用户接口:

x1, x2, x4, 和x8 lanes; 64-bit 和128-bit位宽

Root Port简要介绍

Xilinx FPGAs支持硬核root port,但是没有硬核root complex。root complex包括一个或多个root port、内存,IO子系统等。root port只是提供给switch或者endpoint连接端口。两者之间的关系如下:

root port它通常用于简单的设计,如单个设计endpoint相连。root complex软件环境软件环境和复杂的设计。

FPGA构建root port常见案例如下:

FPGA构建root complex常见案例如下:

root port与endpoint也有许多不同之处。root port使用Type 配置头部空间。endpoint使用Type 0配置头空间。两者的主要区别如下:

PCIE协议简述

PCIE的地址空间

PCI Express实现了四个地址空间:

1、PCIe配置空间(多达4KB)

– 必须有,每一个PCI所有设备都有其映射到内存的配置空间

– 前256字节与PCI兼容

2、PCIe内存映射空间

– 根据设备功能选择是否需要映射内存空间

3、PCIe IO映射空间

– 可选的

4、PCIe消息空间

其中PCIe内存映射空间主要用于大量数据的传输,IO传输少量数据的映射空间。

Type0型:

– 端点设备的配置

– 配置预定义由根复合体发起PCI系统端点设备头部区域

– 设备号/ID

– BAR

Type1型:

– 用于配置Switches/Bridges/end point

PCIE TLP包的数据类型

上面已经讲解PCIE分别包括事务层、数据链路层、物理层,每一层对TLP包的作用如下:

这里的3DW与4DW其实是与地址是32位还是64位挂钩。

具体TLP包在每层协议的情况如下:

PCIE中TLP包的类型如下:

PCIE的路由类型

PCIE每一种请求或者完成报文头都会有类型标注,每个数据包的路由都基于以下三种方式:

1、 地址路由

2、 ID 路由

3、 隐含式路由

端点的地址路由

端点设备检查TLP包中的地址与BAR中所有地址进行比较,如果不属于本端点范围,则拒绝。

端点的ID路由

端点设备检查TLP包里的 总线 ID 和 设备 ID 功能ID是否与本端点一致,这些信息在Type0的配置信息里可以捕获。

不同类型的TLP包与路由类型的对应关系如下:

PCIE点对点的传输框图

1、配置IO传输

2、DMA传输

3、end point与end piont之间的传输

PCIE的中断类型

PCIE的中断类型主要有两种:

1、MSI:消息中断

2、INTx:引脚中断

真正的PCIe设备:必须使用MSI发送中断,可选择性地支持INTx消息。

PCI设备:必须支持INTx消息

PCIE的理论带宽

Gen2单向链路速率5Gbps

1、 使用8B/10B编码,产生20%的数据开销

2、 理论带宽=链路速率 80% 通道数

3、 对于单通道:

– Gen1: 2.5Gbps0.8=250MBps

– Gen2: 5Gbps0.8=500MBps

– Gen3: 8Gbps*1=1GBps

4、 更多的开销是由协议导致

– 数据头

– 校验位

– 链路训练

– 错误通信

TLP包格式简述

上面我们已经讲解了TLP包常见的类型,那么这部分内容讲解每种TLP包的具体格式。

一个TLP包的格式如下:

每位的详细信息如下:

接下来对上面的每一位进行粗略的介绍。

1、Fmt :用来指明TLP包是3DW还是4DW

2、Type :用来确定TLP包的类型,

Memory read or write

Completion packet

Configuration packet

Message

3、Traffic Class:除了MemoryRead/Write TLPs必须是零,一般情况是默认为0

4、Attr :包含有关处理事务时核心行为的特定信息

5、TD :当该位位1是,TLP包中包括CRC检验,为零时不包括CRC校验

6、EP :指示此TLP包含错误且应忽略

7、AT :地址类型,一般默认为零即可。

Default/Untranslated (00)

Translation Request (10)

Translated (11)

8、Length Field :描述TLP包种有效数据的长度,注意单位时DW,最大长度时1024个DW长度

9、First/Last Byte Enables:四位中的每一位分别对应TLP包中的第一个DW和最后一个DW中的每个字节是否有效。一个DW正好也是4个字节。

Memory Write TLP Header格式

Memory Write TLP Header格式如下:

3DW的TLP包头:

4DW的TLP包头:

1、Requester ID:包括bus, device, and function numbers这些在ID路由的时候时必备信息

2、Tag :由用户定义,具体的内容与作用,用户进行商议。

3、Address:byte address,最低的两位总是零对齐到DWord寻址。

Memory Read TLP Header格式

Memory Read TLP Header格式如下:

3DW的TLP包头:

4DW的TLP包头:

1、Tag – 这里得Tag主要用于返回得CplDs包得重组,因为饭回来得完成包不一定是按照顺序返回的。

这里没有什么新的位介绍,在前面我们已经介绍完毕。

Memory Read 是 Non‐Posted:

Non‐Posted的请求总是生成一个完成包来回应。除非出现错误,否则Posted的请求永远不会生成完成包。一般的MRd会产生一个带有数据包的完成。一个读请求可以生成一个或多个完成包。

Completions TLPs格式

1、Tag :这里需要注意Tag标志主要是为了接收端按照发送的顺序组包

2、Lower Address :指示第一个启用的数据字节的字节地址的低位,较低的地址和长度不能跨越一个RCB

RCB: Read Completion Boundary

3、Byte count :表示在满足请求之前剩余的字节数

4、Completion status :只是完成包的状态:

Successful completion (“000”)

Unsupported request (“001”)

Configuration request retry status (“010”)

Completer abort (“100”)

5、Requester ID :请求CplD的设备的ID(bus, device, function)

6、Completer ID :正在构建CplD的设备的ID(bus, device, function)

返回的时候必须是RCB的整数倍。而且第一个要与RCB对齐,且不能超过MPS,这里给出一个官方的示例:

示例1:

示例2:

题目:

解答:

Message/Message with Data TLP格式

因为一般用不到我们进行手动组信息包,所以这里我们也就不详细介绍。

PCIE IP核配置需要的注意点

这里简单介绍一下PCIE核配置过程中的注意点,这次我们先不使用XDMA IP,使用下面的PCIE IP:

为了尽可能多的了解PCIE IP中的细节,我们选择高级IP定制:

1、选择高级IP定制,供用户选择的功能增多

2、这里可以选择这个PCIE IP核是当作endpoint还是root port来使用

3、这是指明这个PCIE IP再硬件中的位置编号

4、指明PCIE的lanes数目

5、指明一条lanes的最大通信速度

6、将PCIE转换成AXI4协议的时钟

7、将PCIE转换成AXI4协议的数据位宽

8、PCIE IP的参考频率

1、厂商ID,专属于Xilinx的PCIE的ID,是固定的。

2、设备ID,与厂商ID一起指明数据的类型,被使用选择PCIE上位机的软件驱动。

3、版本ID,指明使用该PCIE IP进行设置的版本

4、子厂商ID,用来更近一步的区分Xilinx旗下的厂商

5、子系统ID,用来识别板卡的的ID

上面的值一般默认即可,不需要做太多的处理

1、选择使能Bar空间。这里需要注意的是,root port对于endpoint的访问只能访问bar空间,而endpoint对root port的读写操作可以访问整个内存。

2、选择Bar的地址是32位还是64位,空间大小一般选择1K即可,只是用来传输一些命令。其值的大小与空间大小有关,具体的关系这里不清楚。

上面整个设置,再PCIE的头配置空间中均有体现:

1、这里可以加上buffer进行优化,其余的默认即可。

1、这里我们一般不选择共享逻辑

1、引脚中断,传统意义下的中断,在PCIE中基本上不再使用

2、消息中断,在PCIE中较为常用

参考文献

[1]、V3学院

总结

由于水平有限,对PCIE的认识不到位,文章中的阐述有可能存在错误,欢迎大家指正。

*声明:本文于网络整理,版权归原作者所有,如来源信息有误或侵犯权益,请联系我们删除或授权事宜。

‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧ END ‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧

NOW现在行动!————— END —————

有你想看的精彩

听大神聊FPGA设计:豁然开朗

ADC/DAC设计经典问答

基于FPGA的快速傅立叶变换

Google版「鸿蒙」,Fuchsia悄悄地来了

日本断供光刻胶,国产迎头赶上!100页国产光刻胶研究框架PPT!

耗时两年,19岁小伙采用230片纯74逻辑芯片搭建出32位Risc-V处理器!可玩贪吃蛇

SPI怎么玩?搞懂时序,运用自如

谈谈Xilinx FPGA设计的实现过程

Verilog_实现任意占空比、任意分频的方法

【FPGA】几种时序问题的常见解决方法

开源DIY墨水屏手表!外观可盐可甜,无线蓝牙计步闹钟一应俱全!

Verilog 版本:Verilog-95、Verilog-2001与System Verilog区别简谈

1202年了,还在使用虚拟机吗?Win10安装Ubuntu子系统及图形化界面详细教程

例说Verilog HDL和VHDL区别,助你选择适合自己的硬件描述语言

FPGA重点知识13条,助你构建完整“逻辑观”之一

FPGA 的重构

ISP(图像信号处理)算法概述、工作原理、架构、处理流程

用Verilog设计一个16 位 RISC 处理器

Xilinx FPGA程序升级详解